AS7C32096A

AS7C32096A is 3.3V 256K x 8 CMOS SRAM manufactured by Alliance Semiconductor.

October 2021

®

3.3V 2Mb (256K × 8) CMOS FAST SRAM

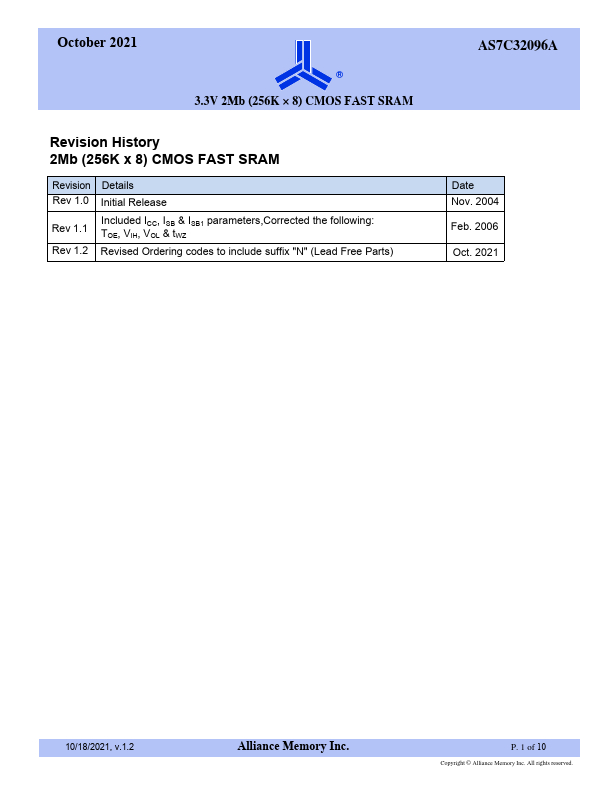

Revision History 2Mb (256K x 8) CMOS FAST SRAM

Revision Details Rev 1.0 Initial Release

Rev 1.1 Rev 1.2

Included ICC, ISB & ISB1 parameters,Corrected the following: TOE, VIH, VOL & tWZ

Revised Ordering codes to include suffix "N" (Lead Free Parts)

Date Nov. 2004 Feb. 2006 Oct. 2021

10/18/2021, v.1.2

Alliance Memory Inc.

P. 1 of 10

Copyright © Alliance Memory Inc. All rights reserved.

October 2021

®

3.3V 2Mb (256K × 8) CMOS FAST SRAM

Features

- Industrial and mercial temperature

- Organization: 262,144 words × 8 bits

- Center power and ground pins

- High speed

- 10/12/15/20 ns address access time

-...