AS7C33128NTD32A Description

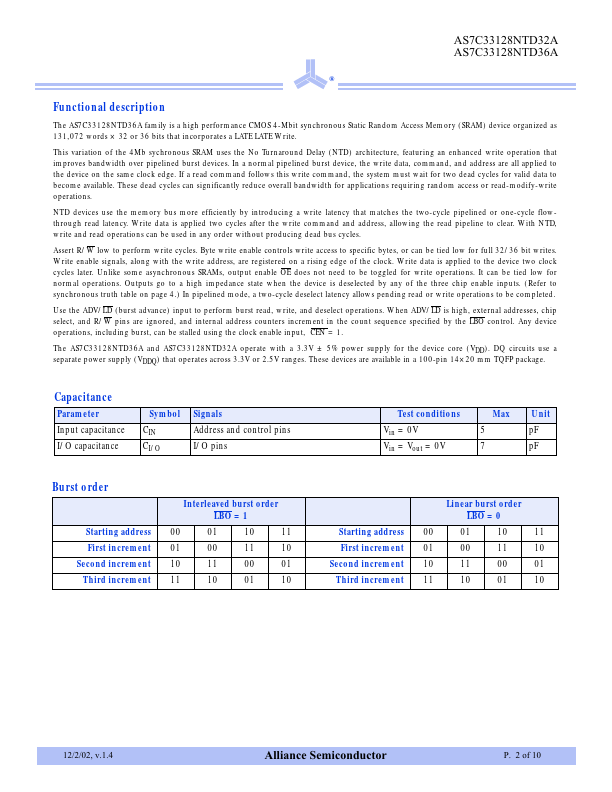

The AS7C33128NTD36A family is a high performance CMOS 4-Mbit synchronous Static Random Access Memory (SRAM) device organized as 131,072 words × 32 or 36 bits that incorporates a LATE LATE Write. This variation of the 4Mb sychronous SRAM uses the No Turnaround Delay (NTD) architecture, featuring an enhanced write operation that improves bandwidth over pipelined burst devices. In a normal pipelined burst device, the...

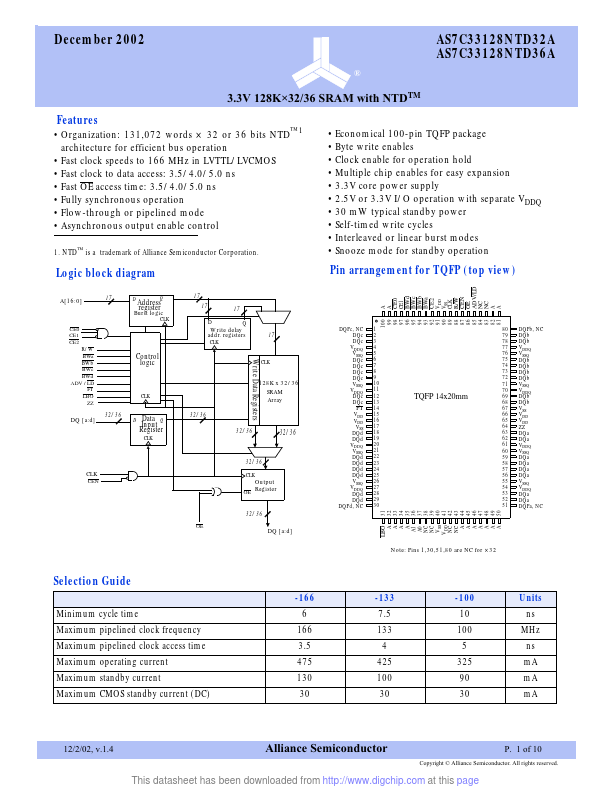

AS7C33128NTD32A Key Features

- Organization: 131,072 words × 32 or 36 bits NTD™1 architecture for efficient bus operation

- Fast clock speeds to 166 MHz in LVTTL/LVCMOS

- Fast clock to data access: 3.5/4.0/5.0 ns

- Fast OE access time: 3.5/4.0/5.0 ns

- Fully synchronous operation

- Flow-through or pipelined mode

- Asynchronous output enable control

- Economical 100-pin TQFP package

- Byte write enables

- Clock enable for operation hold