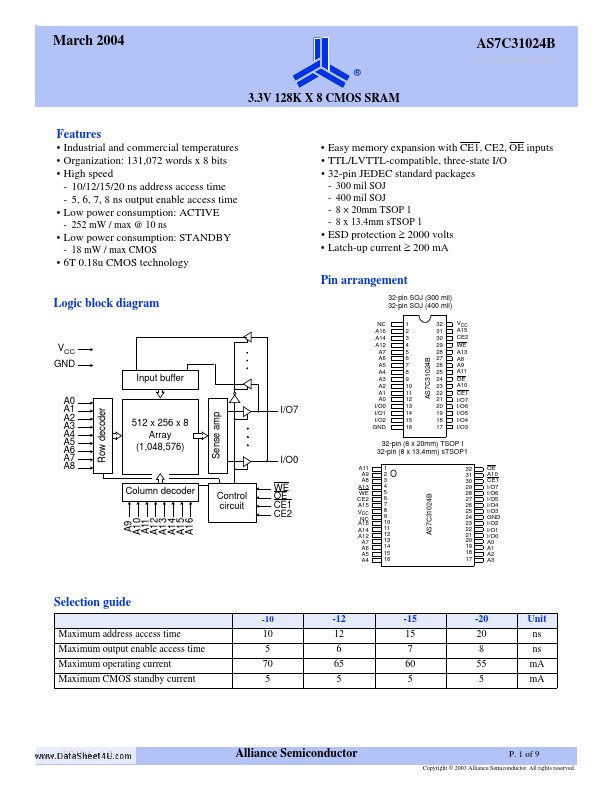

AS7C31024B

Key Features

- Industrial and mercial temperatures

- High speed - 10/12/15/20 ns address access time - 5, 6, 7, 8 ns output enable access time

- Low power consumption: ACTIVE

- 252 mW / max @ 10 ns

- Easy memory expansion with CE1, CE2, OE inputs

- 32-pin JEDEC standard packages 300 mil SOJ 400 mil SOJ 8 × 20mm TSOP 1 8 x 13.4mm sTSOP 1

- Low power consumption: STANDBY

- 18 mW / max CMOS

- ESD protection ≥ 2000 volts

- Latch-up current ≥ 200 mA