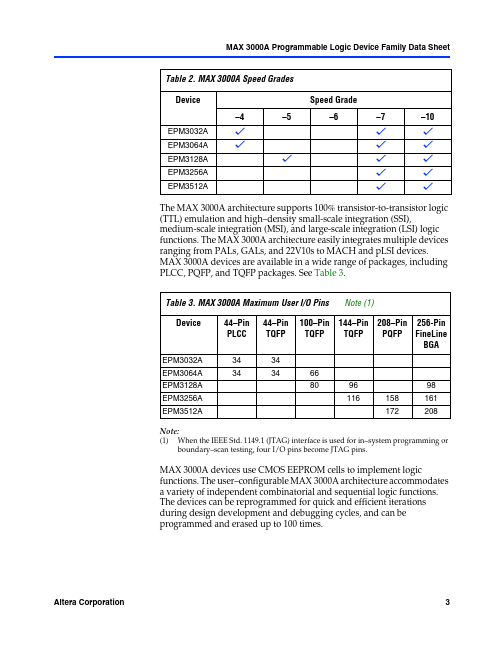

EPM3512A Description

PCI patible Bus friendly architecture including programmable slew rate control Open drain output option Programmable macrocell flipflops with individual clear, preset, clock, and clock enable controls Programmable power saving mode for a power reduction of over 50% in each macrocell Configurable expander product term distribution, allowing up to 32 product terms per macrocell Programmable security bit for protection...

EPM3512A Key Features

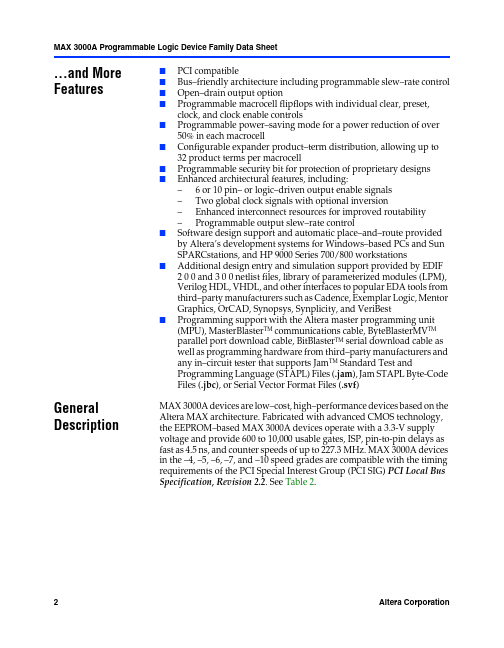

- High-performance, low-cost CMOS EEPROM-based programmable logic devices (PLDs) built on a MAX® architecture (see Table 1

- 3.3-V in-system programmability (ISP) through the built-in IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface wit

- ISP circuitry pliant with IEEE Std. 1532

- Built-in boundary-scan test (BST) circuitry pliant with IEEE Std. 1149.1-1990

- Enhanced ISP features

- Enhanced ISP algorithm for faster programming

- ISP_Done bit to ensure plete programming

- Pull-up resistor on I/O pins during in-system programming

- High-density PLDs ranging from 600 to 10,000 usable gates

- MultiVoltTM I/O interface enabling the device core to run at 3.3 V