AD14160 Description

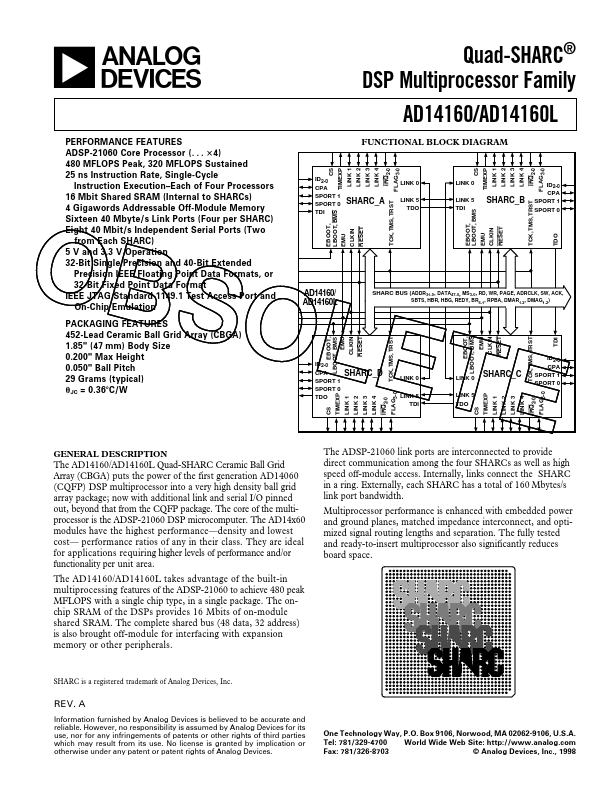

The AD14160/AD14160L Quad-SHARC Ceramic Ball Grid Array (CBGA) puts the power of the first generation AD14060 (CQFP) DSP multiprocessor into a very high density ball grid array package; now with additional link and serial I/O pinned out, beyond that from the CQFP package. The core of the multiprocessor is the ADSP-21060 DSP microputer.