AD14160L

AD14160L is manufactured by Analog Devices.

a

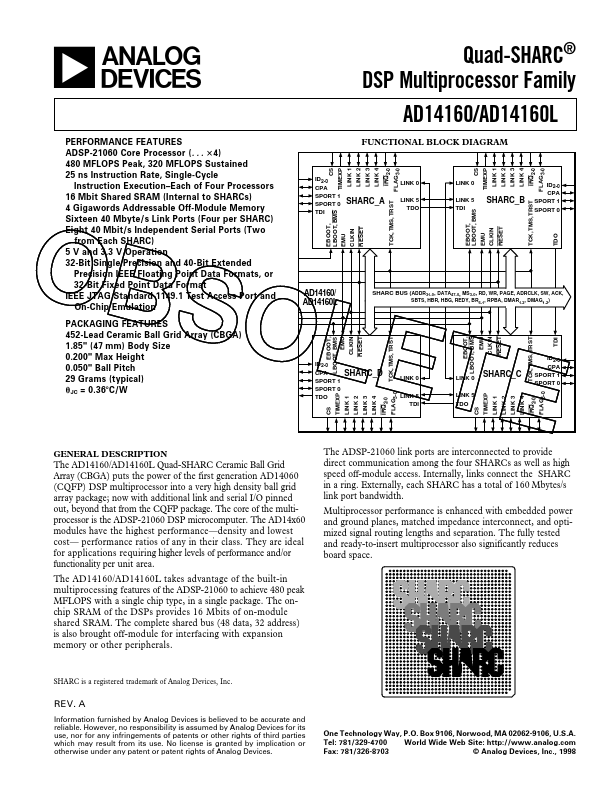

Quad-SHARC® DSP Multiprocessor Family

AD14160/AD14160L

PERFORMANCE Features

FUNCTIONAL BLOCK DIAGRAM

ADSP-21060 Core Processor (. . . ؋4)

480 MFLOPS Peak, 320 MFLOPS Sustained

CS TIMEXP

LINK 1 LINK 2 LINK 3 LINK 4 IRQ2-0 FLAG3-0

CS TIMEXP

LINK 1 LINK 2 LINK 3 LINK 4 IRQ2-0 FLAG3-0

25 ns Instruction Rate, Single-Cycle Instruction Execution- Each of Four Processors

ID2-0 CPA

LINK 0

LINK 0

ID2-0

EBOOT, LBOOT, BMS EMU CLKIN RESET TCK, TMS, TRST

EBOOT, LBOOT, BMS EMU CLKIN RESET TCK, TMS, TRST

16 Mbit Shared SRAM (Internal to SHARCs) 4 Gigawords Addressable Off-Module Memory

SPORT 1

SPORT 0 SHARC_A

LINK 5 TDO

LINK 5 TDI

SHARC_B SPORT 1

SPORT 0

Sixteen 40 Mbyte/s...