AD1895

AD1895 is 192 kHz Stereo Asynchronous Sample Rate Converter manufactured by Analog Devices.

FEATURES

Automatically Senses Sample Frequencies No Programming Required Attenuates Sample Clock Jitter 3.3 V- 5 V Input and 3.3 V Core Supply Voltages Accepts 16-/18-/20-/24-Bit Data Up to 192 k Hz Sample Rate Input/Output Sample Ratios from 7.75:1 to 1:8 Bypass Mode Multiple AD1895 TDM Daisy-Chain Mode 128 d B Signal-to-Noise and Dynamic Range (A-Weighted, 20 Hz- 20 k Hz BW) Up to

- 122 d B THD + N Linear Phase FIR Filter Hardware Controllable Soft Mute Supports 256 ؋ f S, 512 ؋ f S or 768 ؋ f S Master Mode Clock Flexible Three-Wire Serial Data Port with Left-Justified, I2S, Right-Justified (16-, 18-, 20-, 24-Bits), and TDM Serial Port Modes Master/Slave Input and Output Modes 28-Lead SSOP Plastic Package APPLICATIONS Home Theater Systems, Automotive Audio Systems, DVD, DVD-R, CD-R, Set-Top Boxes, Digital Audio Effects Processors

192 k Hz Stereo Asynchronous Sample Rate Converter AD1895-

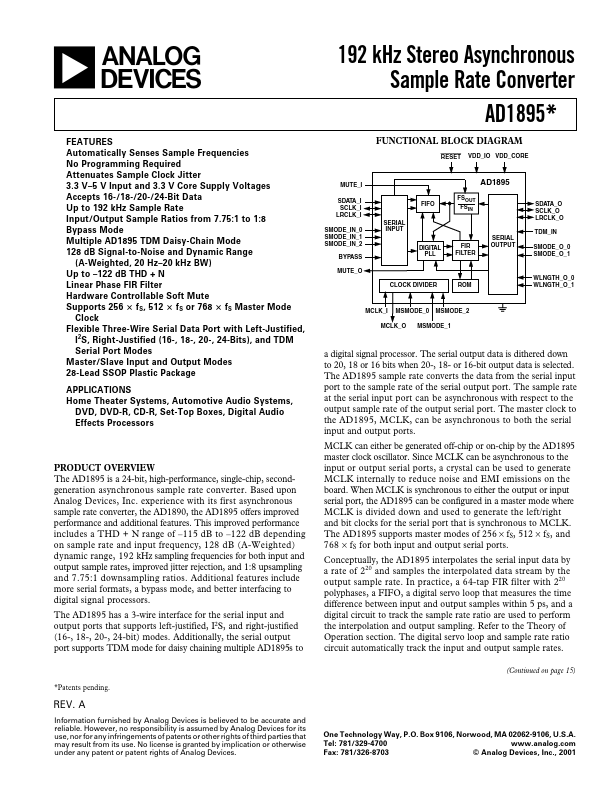

FUNCTIONAL BLOCK DIAGRAM

RESET VDD_IO VDD_CORE MUTE_I SDATA_I SCLK_I LRCLK_I SMODE_IN_0 SMODE_IN_1 SMODE_IN_2 BYPASS MUTE_O CLOCK DIVIDER ROM WLNGTH_O_0 WLNGTH_O_1 SERIAL INPUT DIGITAL PLL FIR FILTER SERIAL OUTPUT FIFO FSOUT FSIN

SDATA_O SCLK_O LRCLK_O TDM_IN SMODE_O_0 SMODE_O_1

MCLK_I

MSMODE_0

MSMODE_2

MCLK_O

MSMODE_1 a digital signal processor. The serial output data is dithered down to 20, 18 or 16 bits when 20-, 18- or 16-bit output data is selected. The AD1895 sample rate converts the data from the serial input port to the sample rate of the serial output port. The sample rate at the serial input port can be asynchronous with respect to the output sample rate of the output serial port. The master clock to the AD1895, MCLK, can be asynchronous to both the serial input and output ports. MCLK can either be generated off-chip or on-chip by the AD1895 master clock oscillator. Since MCLK can be asynchronous to the input or output serial ports, a crystal can be used to generate MCLK internally to reduce noise and EMI emissions on the board. When MCLK is synchronous to either...