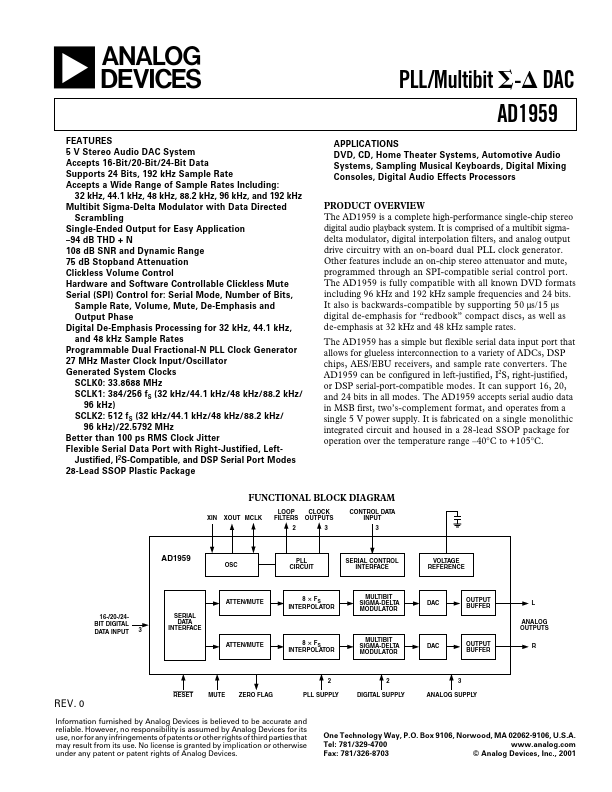

| Part | AD1959 |

|---|---|

| Description | PLL/Multibit DAC |

| Manufacturer | Analog Devices |

| Size | 108.00 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| ES9039Q2M | ESS Technology | 32-bit High performance 2-Channel DAC |

| CS43198 | Cirrus Logic | 32-Bit High-Performance DAC |

| ES9039PRO | ESS Technology | 32-bit High-Performance 8-Channel DAC |