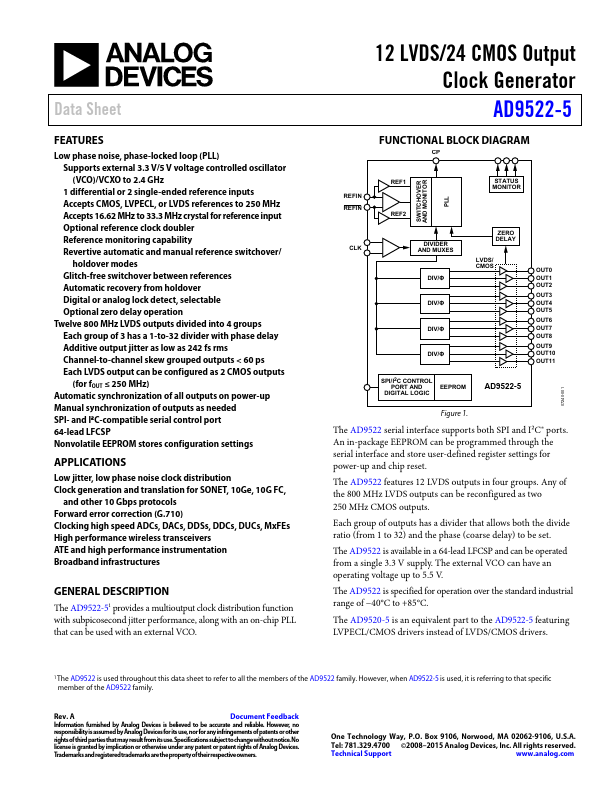

- Part: AD9522-5

- Description: 12 LVDS/24 CMOS Output Clock Generator

- Manufacturer: Analog Devices

- Size: 1.32 MB

Related Analog Devices Datasheets

| Part Number | Description |

|---|---|

| AD9522-0 | 12 LVDS/24 CMOS Output Clock Generator |

| AD9522-1 | 12 LVDS/24 CMOS Output Clock Generator |

| AD9522-2 | 12 LVDS/24 CMOS Output Clock Generator |

| AD9522-3 | 12 LVDS/24 CMOS Output Clock Generator |

| AD9522-4 | 12 LVDS/24 CMOS Output Clock Generator |