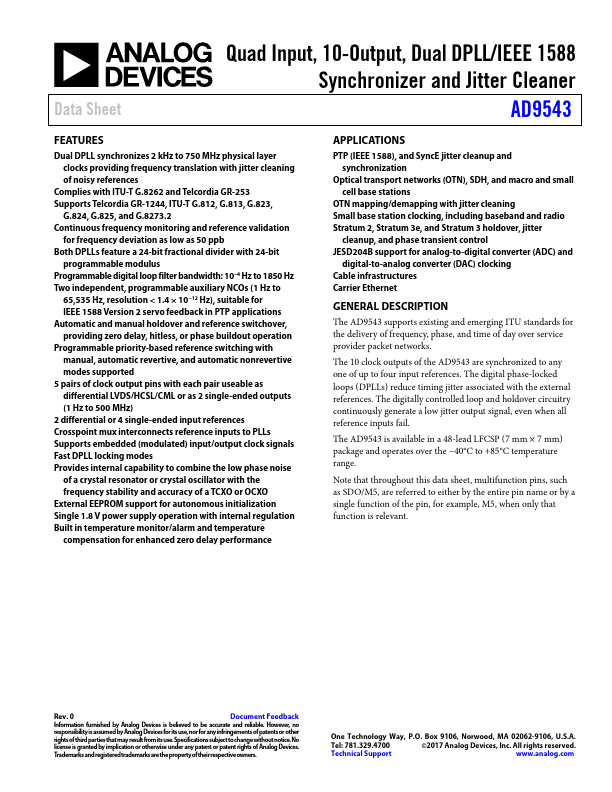

| Part | AD9543 |

|---|---|

| Description | Dual DPLL/IEEE 1588 Synchronizer and Jitter Cleaner |

| Manufacturer | Analog Devices |

| Size | 1.27 MB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| LMK04610 | Texas Instruments | Ultra-Low Noise and Low Power JESD204B Compliant Clock Jitter Cleaner |

| CDCM6208 | Texas Instruments | Jitter Cleaner |

| AD9524 | Analog Devices | Jitter Cleaner and Clock Generator |