AD9652 Overview

Key Specifications

Mount Type: PCB

Max Operating Temp: 85 °C

Min Operating Temp: -40 °C

Description

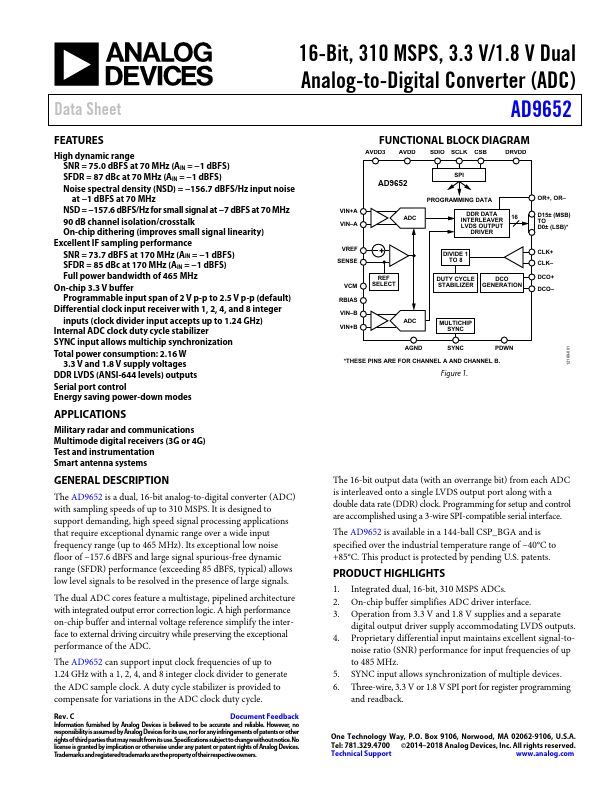

The AD9652 is a dual, 16-bit analog-to-digital converter (ADC) with sampling speeds of up to 310 MSPS. It is designed to support demanding, high speed signal processing applications that require exceptional dynamic range over a wide input frequency range (up to 465 MHz).