ADF4001 Overview

Key Specifications

Package: LFCSP EP

Mount Type: Surface Mount

Pins: 20

Operating Voltage: 5 V

Description

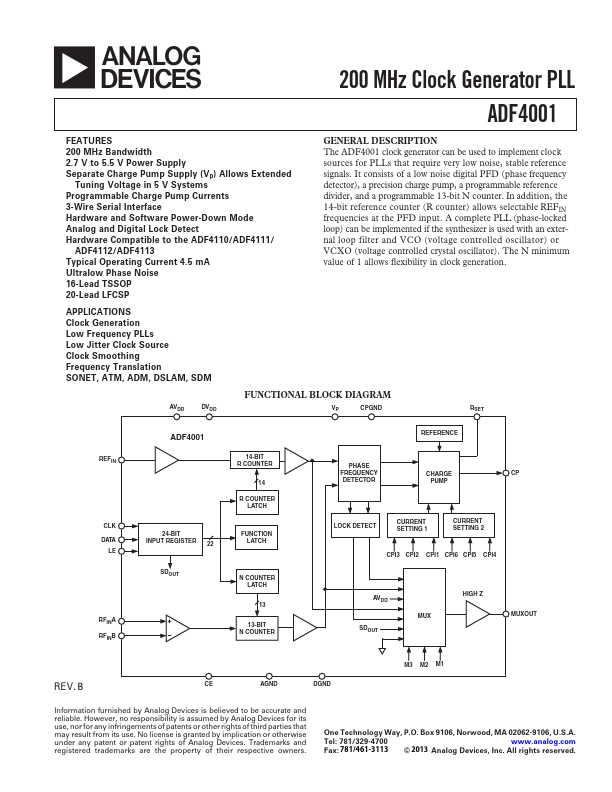

The ADF4001 clock generator can be used to implement clock sources for PLLs that require very low noise, stable reference signals. It consists of a low noise digital PFD (phase frequency detector), a precision charge pump, a programmable reference divider, and a programmable 13-bit N counter.