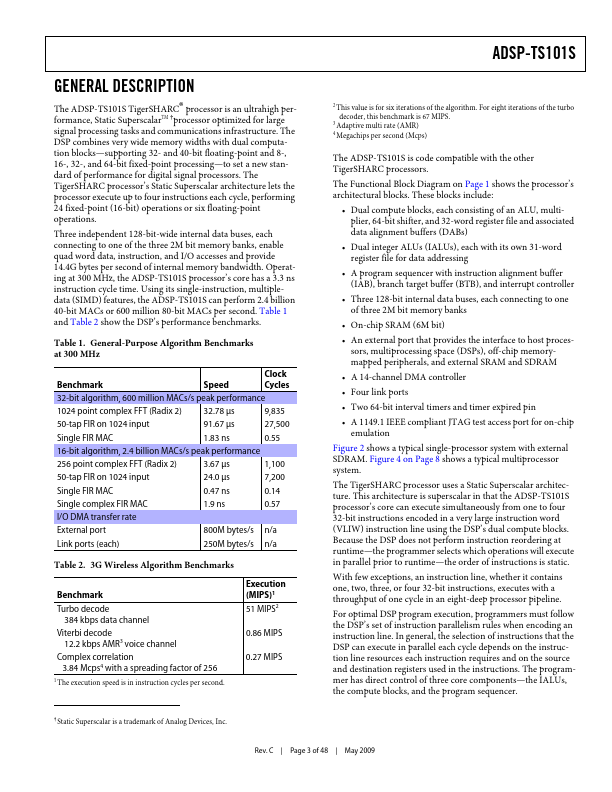

Datasheet Summary

.. a

KEY Features

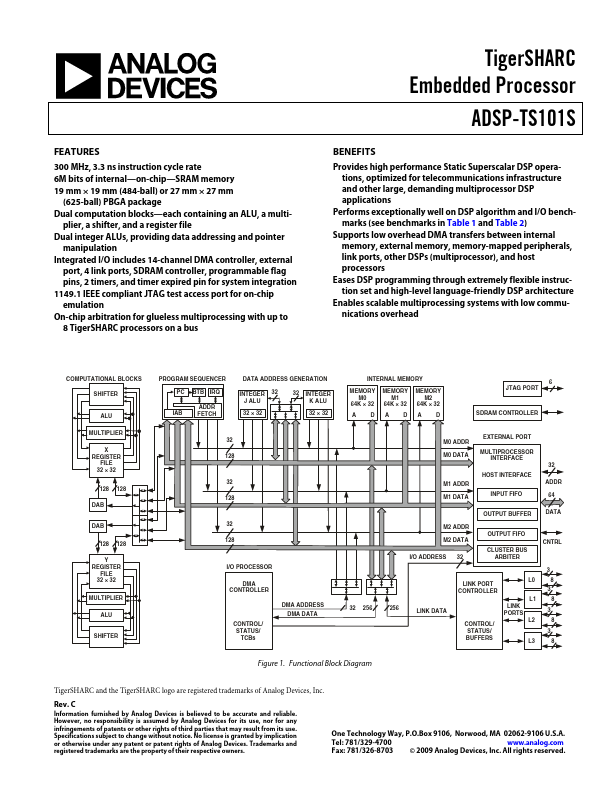

300 MHz, 3.3 ns Instruction Cycle Rate 6M Bits of Internal- On-Chip- SRAM Memory 19 mm ؋ 19 mm (484-Ball) or 27 mm ؋ 27 mm (625-Ball) PBGA Package Dual putation Blocks- Each Containing an ALU, a Multiplier, a Shifter, and a Register File Dual Integer ALUs, Providing Data Addressing and Pointer Manipulation Integrated I/O Includes 14 Channel DMA Controller, External Port, Four Link Ports, SDRAM Controller, Programmable Flag Pins, Two Timers, and Timer Expired Pin for System Integration 1149.1 IEEE pliant JTAG Test Access Port for On-Chip Emulation On-Chip Arbitration for Glueless Multiprocessing with up to Eight TigerSHARC Processors on a Bus

Embedded...