AZ100LVE210

AZ100LVE210 is ECL/PECL 1:4 / 1:5 Differential Clock Driver manufactured by Arizona Microtek.

..

ARIZONA MICROTEK, INC.

ECL/PECL 1:4, 1:5 Differential Clock Driver Features

- -

- -

- -

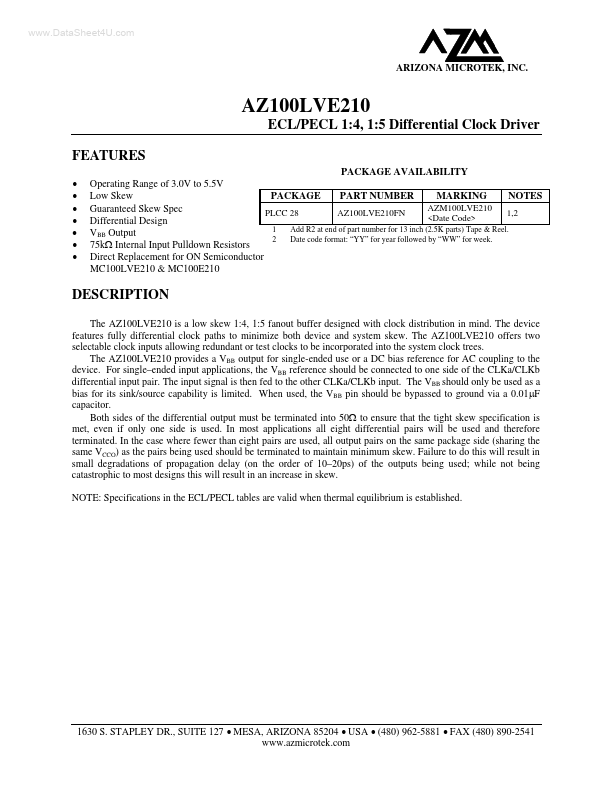

- PACKAGE AVAILABILITY Operating Range of 3.0V to 5.5V PACKAGE PART NUMBER MARKING NOTES Low Skew AZM100LVE210 Guaranteed Skew Spec PLCC 28 AZ100LVE210FN 1,2 <Date Code> Differential Design 1 Add R2 at end of part number for 13 inch (2.5K parts) Tape & Reel. VBB Output 2 Date code format: “YY” for year followed by “WW” for week. 75kΩ Internal Input Pulldown Resistors Direct Replacement for ON Semiconductor MC100LVE210 & MC100E210

DESCRIPTION

The AZ100LVE210 is a low skew 1:4, 1:5 fanout buffer designed with clock distribution in mind. The device Features fully...