AZP94

AZP94 is Clock Generation Chip manufactured by Arizona Microtek.

..

ARIZONA MICROTEK, INC.

ECL/PECL ÷1, ÷2 Clock Generation Chip with Tristate patible Outputs Features

- -

- -

- -

- -

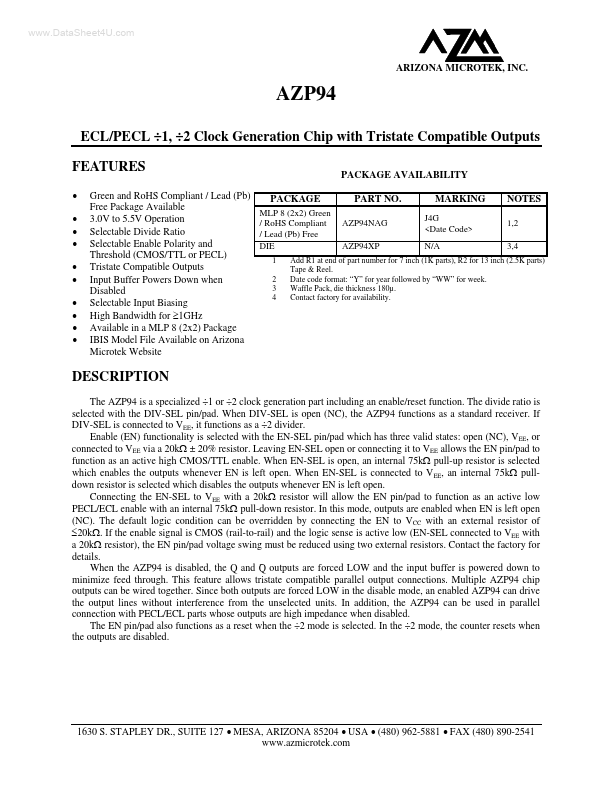

- - Green and RoHS pliant / Lead (Pb) Free Package Available 3.0V to 5.5V Operation Selectable Divide Ratio Selectable Enable Polarity and Threshold (CMOS/TTL or PECL) Tristate patible Outputs Input Buffer Powers Down when Disabled Selectable Input Biasing High Bandwidth for ≥1GHz Available in a MLP 8 (2x2) Package IBIS Model File Available on Arizona Microtek Website PACKAGE

MLP 8 (2x2) Green / RoHS pliant / Lead (Pb) Free DIE

1 2 3 4

PACKAGE AVAILABILITY PART NO.

AZP94NAG AZP94XP

MARKING

J4G <Date Code> N/A

NOTES

1,2 3,4

Add R1 at...