AZP92 Overview

Description

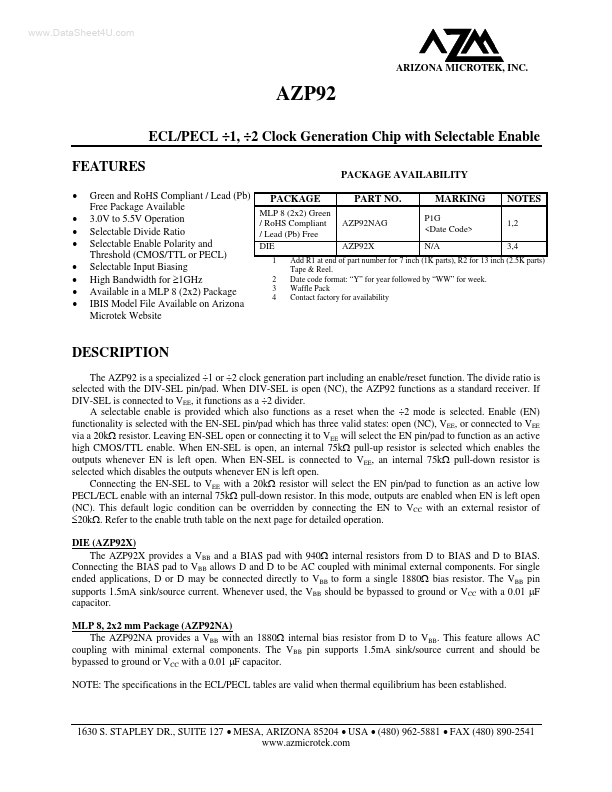

The AZP92 is a specialized ÷1 or ÷2 clock generation part including an enable/reset function. The divide ratio is selected with the DIV-SEL pin/pad.

Key Features

- Date code format: “Y” for year followed by “WW” for week

- Waffle Pack Contact factory for availability