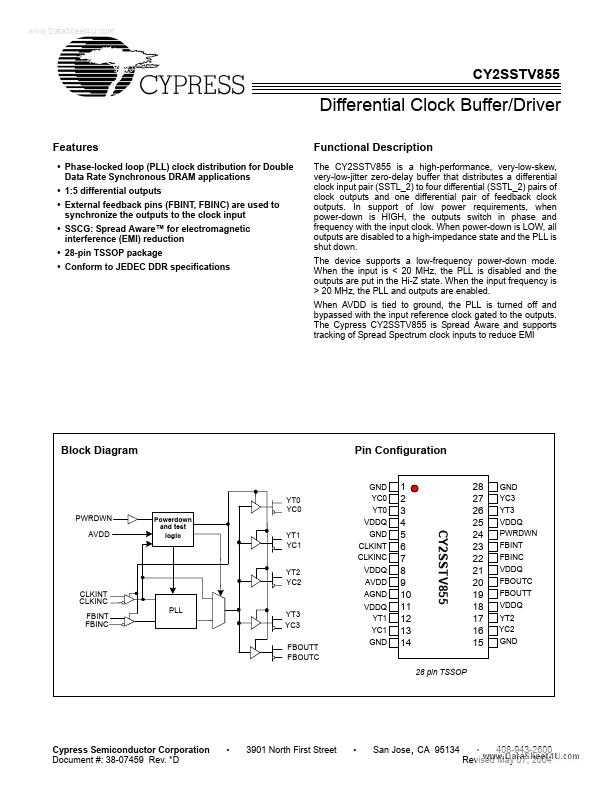

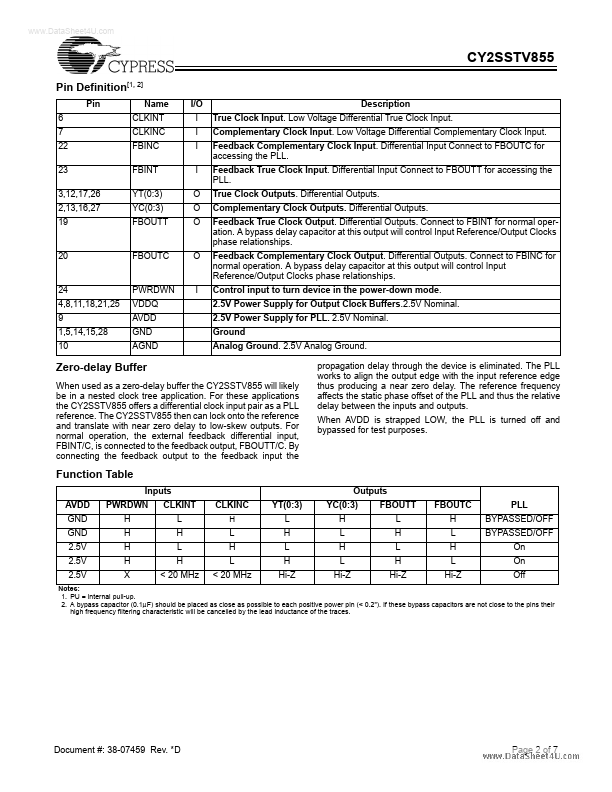

CY2SSTV855 Description

The CY2SSTV855 is a high-performance, very-low-skew, very-low-jitter zero-delay buffer that distributes a differential clock input pair (SSTL_2) to four differential (SSTL_2) pairs of clock outputs and one differential pair of feedback clock outputs. In support of low power requirements, when power-down is HIGH, the outputs switch in phase and frequency with the input clock. When power-down is LOW, all outputs are...

CY2SSTV855 Key Features

- Phase-locked loop (PLL) clock distribution for Double Data Rate Synchronous DRAM