CY2XP306 Key Features

- 60 ps typical Cycle-to-Cycle Jitter

- 30 ps typical Output-Output Skew

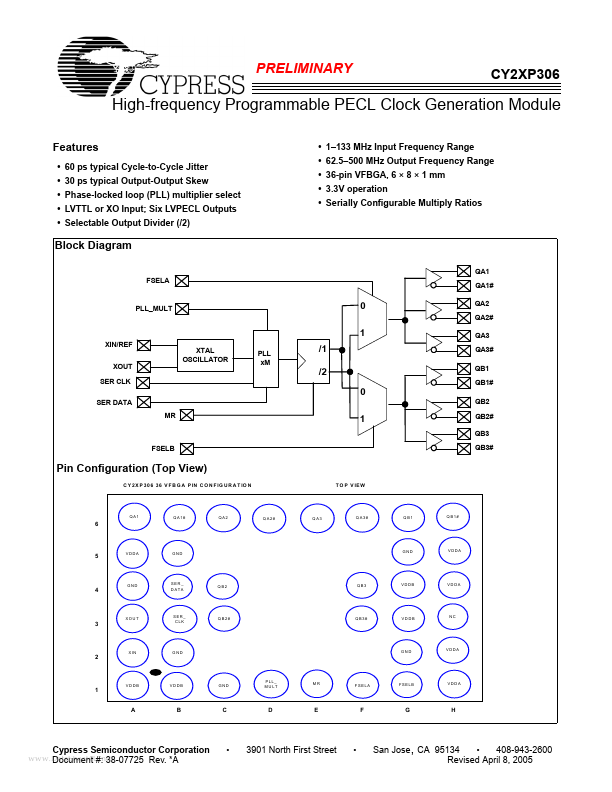

- Phase-locked loop (PLL) multiplier select

- LVTTL or XO Input; Six LVPECL Outputs

- Selectable Output Divider (/2)

- 1-133 MHz Input Frequency Range

- 62.5-500 MHz Output Frequency Range

- 36-pin VFBGA, 6 × 8 × 1 mm

- 3.3V operation

- Serially Configurable Multiply Ratios