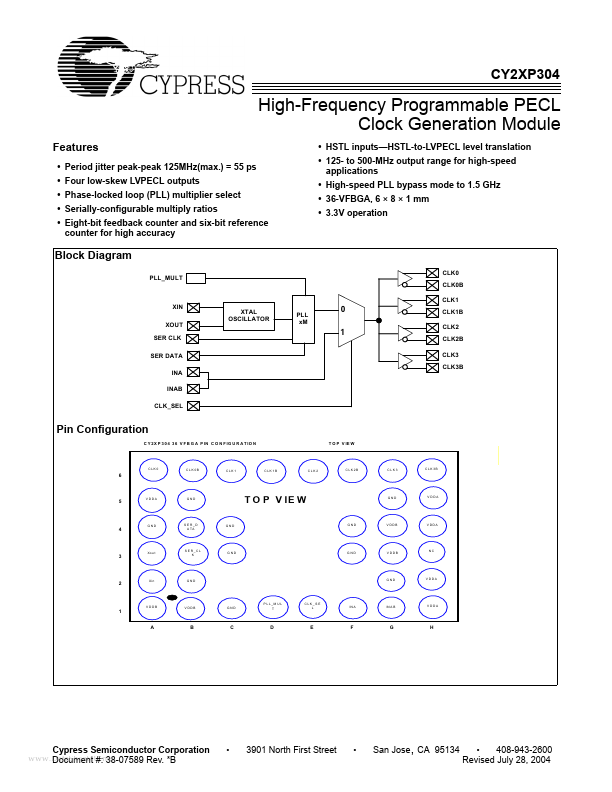

CY2XP304 Description

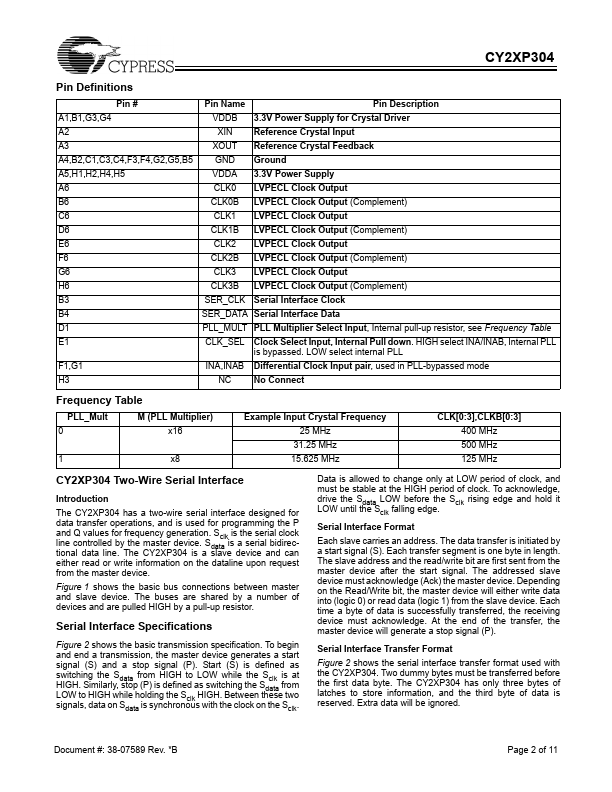

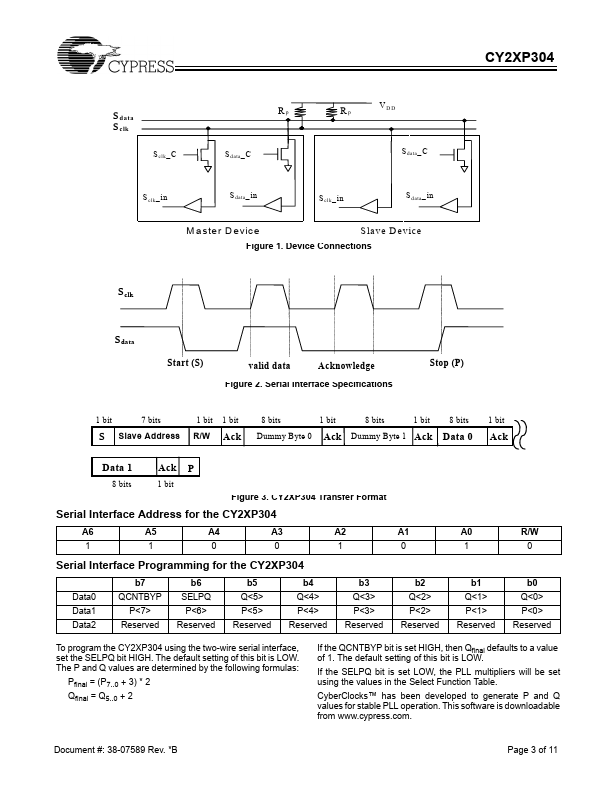

3.3V Power Supply for Crystal Driver SER_CLK Serial Interface Clock SER_DATA Serial Interface Data PLL_MULT PLL Multiplier Select Input, Internal pull-up resistor, see Frequency Table CLK_SEL INA,INAB NC Clock Select Input, Internal Pull down. HIGH select INA/INAB, Internal PLL is bypassed. Sclk is the serial clock line controlled by the master device.

CY2XP304 Key Features

- Period jitter peak-peak 125MHz(max.) = 55 ps

- Four low-skew LVPECL outputs

- Phase-locked loop (PLL) multiplier select

- Serially-configurable multiply ratios

- Eight-bit feedback counter and six-bit reference counter for high accuracy

- HSTL inputs-HSTL-to-LVPECL level translation

- 125- to 500-MHz output range for high-speed

CY2XP304 Applications

- High-speed PLL bypass mode to 1.5 GHz