CY62157DV18

Overview

- Very high speed: 55 ns and 70 ns

- Voltage range: 1.65V to 1.95V

- Pin compatible with CY62157CV18

- Ultra-low active power - Typical active current: 1 mA @ f = 1 MHz - Typical active current: 10 mA @ f = fMAX

- Ultra-low standby power

- Easy memory expansion with CE1, CE2, and OE features

- Automatic power-down when deselected

- CMOS for optimum speed/power

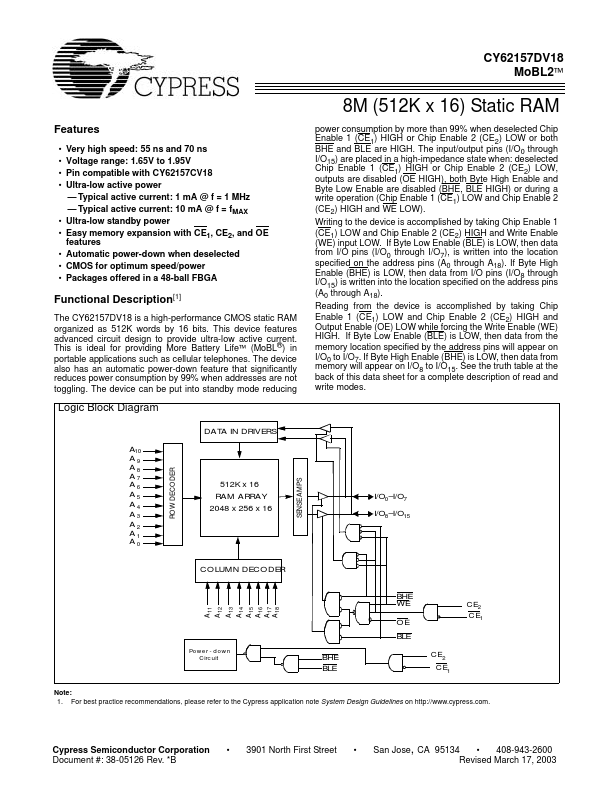

- Packages offered in a 48-ball FBGA Functional Description[1] The CY62157DV18 is a high-performance CMOS static RAM organized as 512K words by 16 bits. This device features advanced circuit design to provide ultra-low active current. This is ideal for providing More Battery Life (MoBL®) in portable applications such as cellular telephones. The device also has an automatic power-down feature that significantly reduces power consumption by 99% when addresses are not toggling. The device can be put into standby mode reducing Logic Block Diagram