Datasheet Summary

..

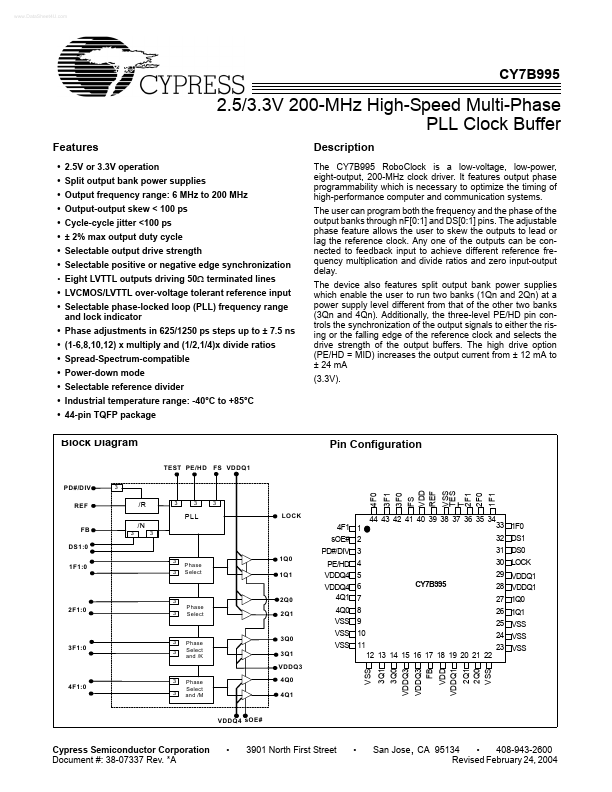

2.5/3.3V 200-MHz High-Speed Multi-Phase PLL Clock Buffer

Features

- 2.5V or 3.3V operation

- Split output bank power supplies

- Output frequency range: 6 MHz to 200 MHz

- Output-output skew < 100 ps

- Cycle-cycle jitter <100 ps

- ± 2% max output duty cycle

- Selectable output drive strength

- Selectable positive or negative edge synchronization

- Eight LVTTL outputs driving 50Ω terminated lines

- LVCMOS/LVTTL over-voltage tolerant reference input

- Selectable phase-locked loop (PLL) frequency range and lock indicator

- Phase adjustments in 625/1250 ps steps up to ± 7.5 ns

- (1-6,8,10,12) x multiply and (1/2,1/4)x divide ratios

- Spread-Spectrum-patible

-...