CY7C09359AV Overview

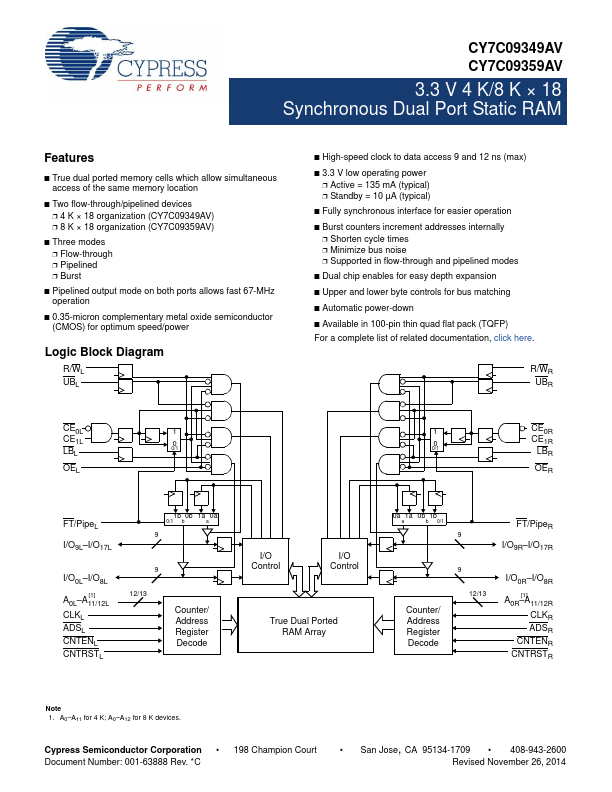

CY7C09359AV3.3 V 4 K/8 K × 18 Synchronous Dual Port Static RAM CY7C09349AV CY7C09359AV 3.3 V 4 K/8 K × 18 Synchronous Dual Port Static RAM 3.3 V 4 K/8 K × 18 Synchronous Dual Port Static.

CY7C09359AV Key Features

- True dual ported memory cells which allow simultaneous access of the same memory location

- Two flow-through/pipelined devices

- 4 K × 18 organization (CY7C09349AV)

- 8 K × 18 organization (CY7C09359AV)

- Three modes

- Flow-through

- Pipelined

- Pipelined output mode on both ports allows fast 67-MHz operation

- 0.35-micron plementary metal oxide semiconductor (CMOS) for optimum speed/power

- High-speed clock to data access 9 and 12 ns (max)