Datasheet Summary

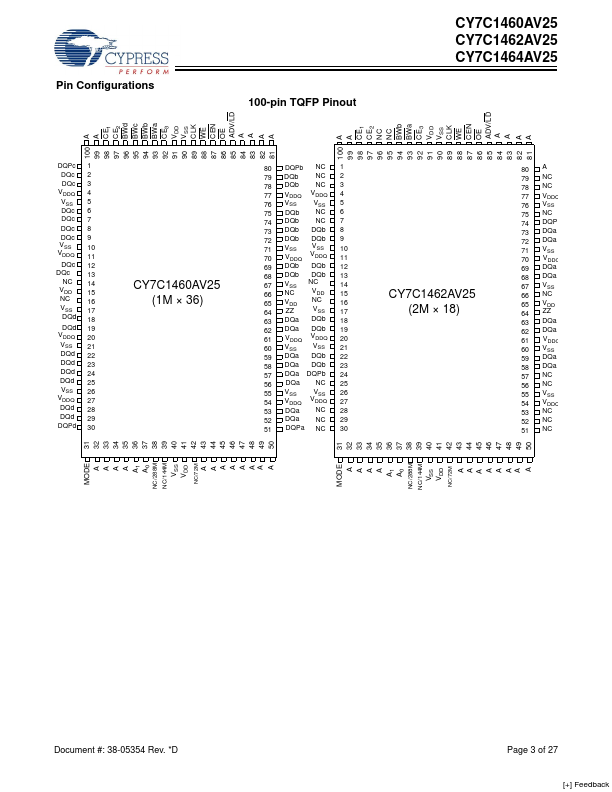

CY7C1460AV25 CY7C1462AV25 CY7C1464AV25

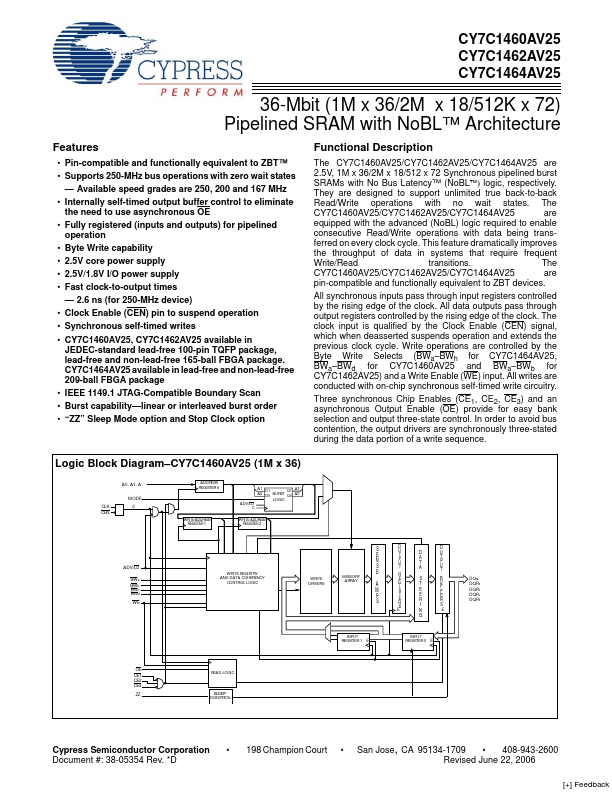

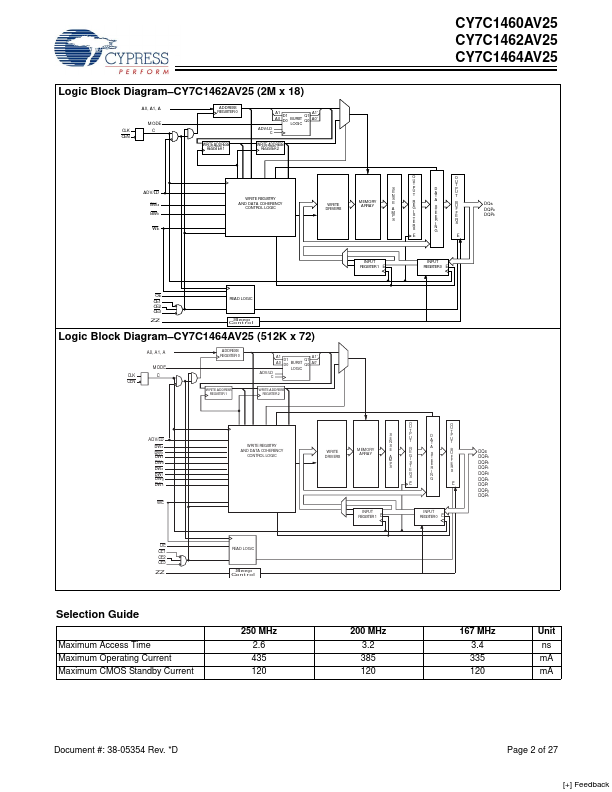

36-Mbit (1M x 36/2M x 18/512K x 72) Pipelined SRAM with NoBL™ Architecture

Features

- Pin-patible and functionally equivalent to ZBT™

- Supports 250-MHz bus operations with zero wait states

- Available speed grades are 250, 200 and 167 MHz

- Internally self-timed output buffer control to eliminate the need to use asynchronous OE

- Fully registered (inputs and outputs) for pipelined operation

- Byte Write capability

- 2.5V core power supply

- 2.5V/1.8V I/O power supply

- Fast clock-to-output times

- 2.6 ns (for 250-MHz device)

- Clock Enable (CEN) pin to suspend operation

- Synchronous self-timed writes

- CY7C1460AV25, CY7C1462AV25 available in...