CYD04S36V Datasheet Text

..

PRELIMINARY

CYD01S36V CYD02S36V/CYD04S36V CYD09S36V/CYD18S36V

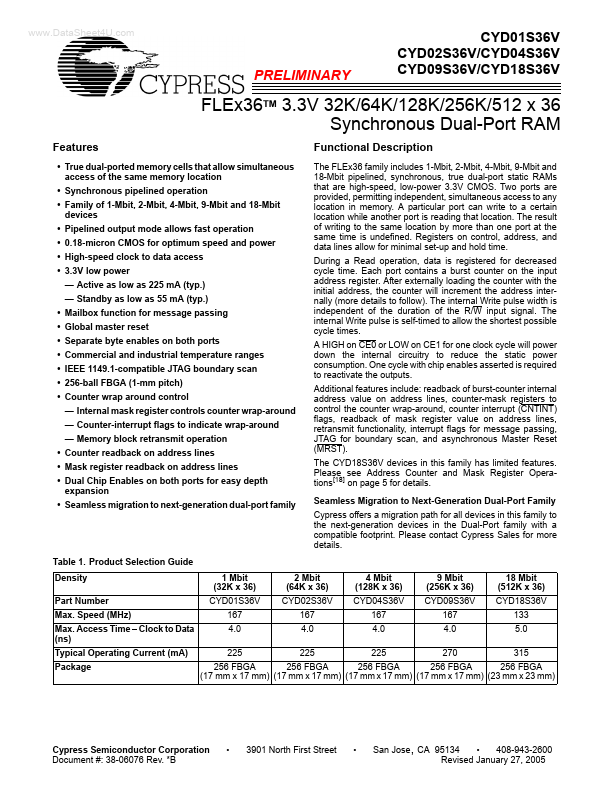

FLEx36TM 3.3V 32K/64K/128K/256K/512 x 36 Synchronous Dual-Port RAM

Features

- True dual-ported memory cells that allow simultaneous access of the same memory location

- Synchronous pipelined operation

- Family of 1-Mbit, 2-Mbit, 4-Mbit, 9-Mbit and 18-Mbit devices

- Pipelined output mode allows fast operation

- 0.18-micron CMOS for optimum speed and power

- High-speed clock to data access

- 3.3V low power

- Active as low as 225 mA (typ.)

- Standby as low as 55 mA (typ.)

- Mailbox function for message passing

- Global master reset

- Separate byte enables on both ports

- mercial and industrial temperature ranges

- IEEE 1149.1-patible JTAG boundary scan

- 256-ball FBGA (1-mm pitch)

- Counter wrap around control

- Internal mask register controls counter wrap-around

- Counter-interrupt flags to indicate wrap-around

- Memory block retransmit operation

- Counter readback on address lines

- Mask register readback on address lines

- Dual Chip Enables on both ports for easy depth expansion

- Seamless migration to next-generation dual-port family

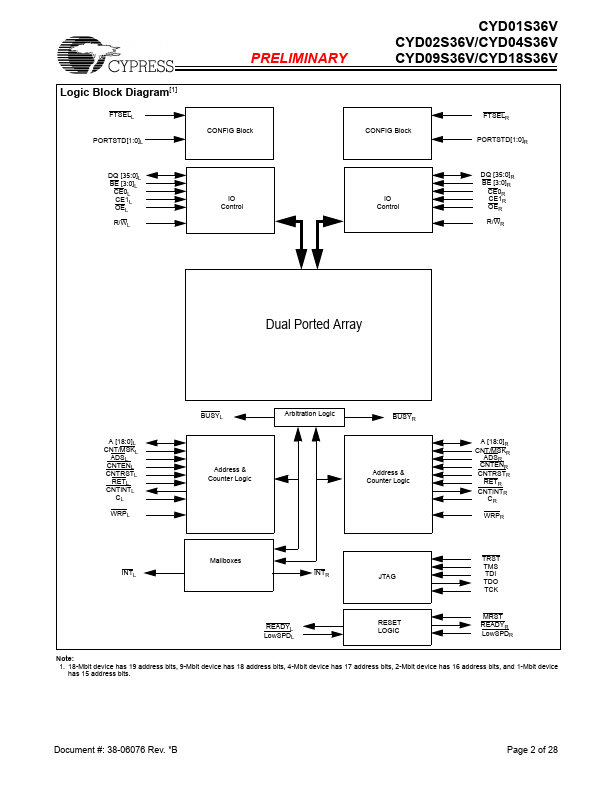

Functional Description

The FLEx36 family includes 1-Mbit, 2-Mbit, 4-Mbit, 9-Mbit and 18-Mbit pipelined, synchronous, true dual-port static RAMs that are high-speed, low-power 3.3V CMOS. Two ports are provided, permitting independent, simultaneous access to any location in memory. A particular port can write to a certain location while another port is reading that location. The result of writing to the same location by more than one port at the same time is undefined. Registers on control, address, and data lines allow for minimal set-up and hold time. During a Read operation, data is registered for decreased cycle time. Each port contains a burst...