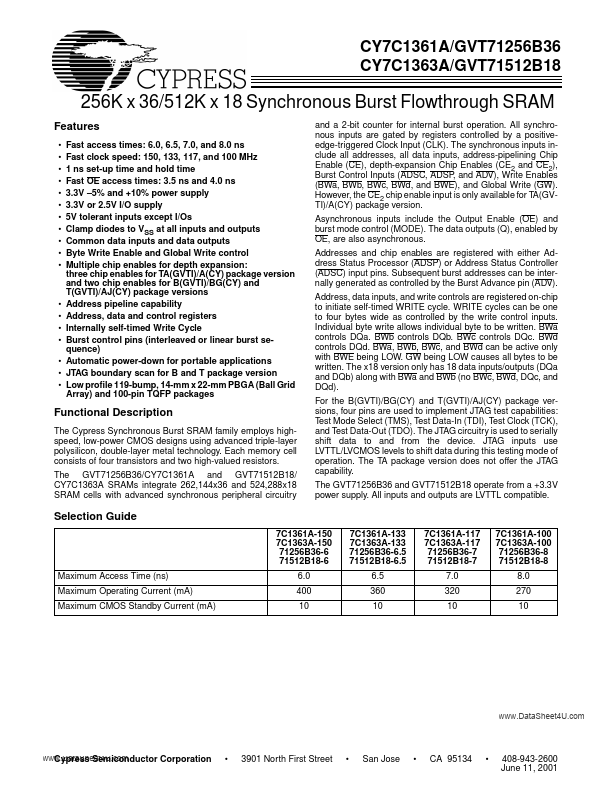

GVT71256B36 Overview

Key Specifications

Package: LQFP

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.63 V

Min Voltage (typical range): 3.135 V

Key Features

- All synchronous inputs are gated by registers controlled by a positiveedge-triggered Clock Input (CLK)

- However, the CE2 chip enable input is only available for TA(GVTI)/A(CY) package version

- Asynchronous inputs include the Output Enable (OE) and burst mode control (MODE)

- The data outputs (Q), enabled by OE, are also asynchronous

- Addresses and chip enables are registered with either Address Status Processor (ADSP) or Address Status Controller (ADSC) input pins