GVT7C1359A Overview

Key Features

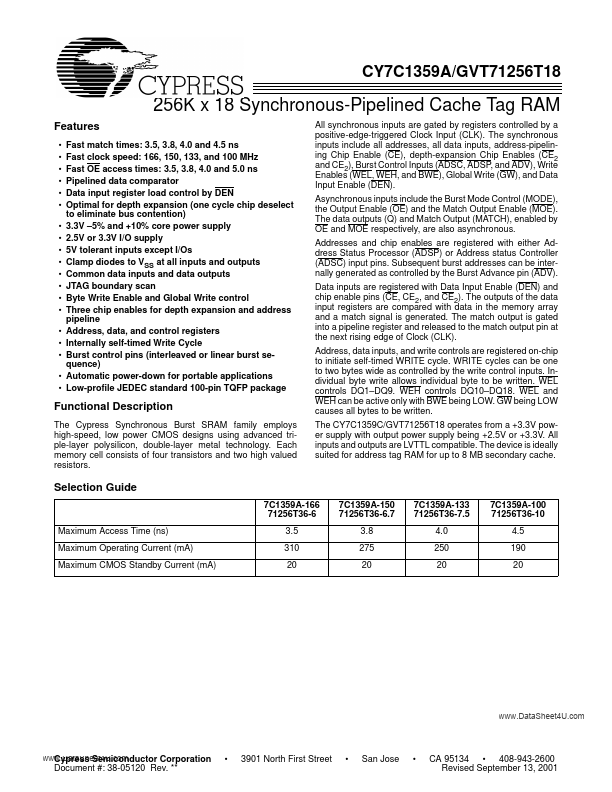

- Asynchronous inputs include the Burst Mode Control (MODE), the Output Enable (OE) and the Match Output Enable (MOE)

- The data outputs (Q) and Match Output (MATCH), enabled by OE and MOE respectively, are also asynchronous

- Addresses and chip enables are registered with either Address Status Processor (ADSP) or Address status Controller (ADSC) input pins

- Subsequent burst addresses can be internally generated as controlled by the Burst Advance pin (ADV)

- Data inputs are registered with Data Input Enable (DEN) and chip enable pins (CE, CE2, and CE2)