DS1350W

DS1350W is 3.3V 4096K Nonvolatile SRAM manufactured by Dallas Semiconductor.

..

PRELIMINARY

DS1350W 3.3V 4096K Nonvolatile SRAM with Battery Monitor

Features

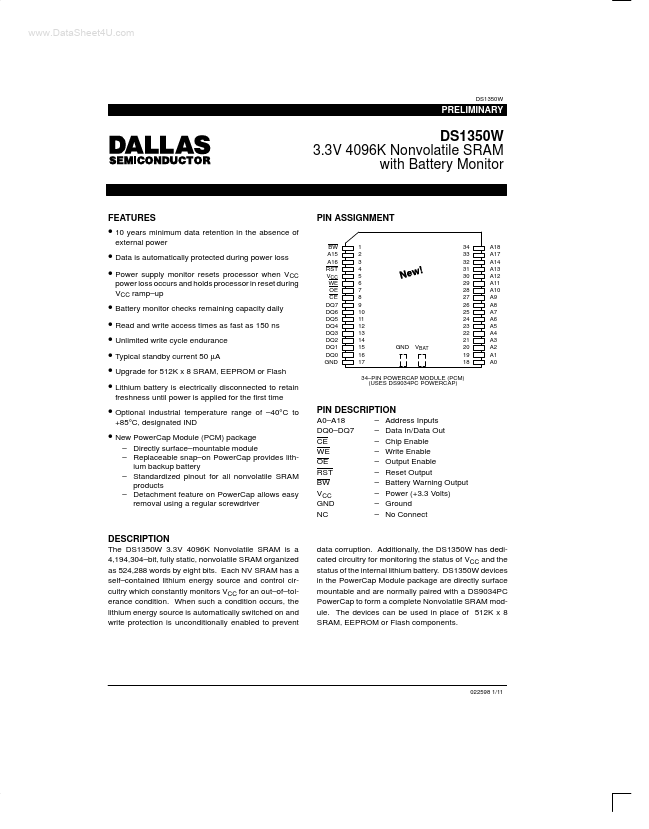

PIN ASSIGNMENT

BW A15 A16 RST VCC WE OE CE DQ7 DQ6 DQ5 DQ4 DQ3 DQ2 DQ1 DQ0 GND 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 34 33 32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 A18 A17 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

- 10 years minimum data retention in the absence of external power

- Data is automatically protected during power loss

- Power supply monitor resets processor when VCC power loss occurs and holds processor in reset during VCC ramp- up

- Battery monitor checks remaining capacity daily

- Read and write access times as fast as 150 ns

- Unlimited write cycle endurance

- Typical standby current 50 µA

- Upgrade for 512K x 8 SRAM, EEPROM or Flash

- Lithium battery is electrically disconnected to retain freshness until power is applied for the first time

VBAT

34- PIN POWERCAP MODULE (PCM) (USES DS9034PC POWERCAP)

- Optional industrial temperature range of

- 40°C to +85°C, designated IND

- Directly surface- mountable module

- Replaceable snap- on Power Cap provides lithium backup battery

- Standardized pinout for all nonvolatile SRAM products

- Detachment feature on Power Cap allows easy removal using a regular screwdriver

PIN DESCRIPTION

A0- A18 DQ0- DQ7 CE WE OE RST BW VCC GND NC

- -

- -

- -

- -

- - Address Inputs Data In/Data Out Chip Enable Write Enable Output Enable Reset Output Battery Warning Output Power (+3.3 Volts) Ground No...