DS1481 Description

The device is normally used in conjunction with a parallel port controller to provide the necessary interface to the host processor. Busy signals allow the host processor to perform other tasks while 1 wire “time slots” are pleted. The DS1481 also saves the state of D/CLK and RES allowing print spoolers to operate without affecting 1 wire munication.

DS1481 Key Features

- Provides a synchronous interface to Dallas Semiconductor 1-wire devices

- patible with low power parallel ports

- Can be cascaded with other DS1481’s

- Allows print spooler and other processes to run during

- Provides

- Space saving 14-pin (150 mil), SOIC package

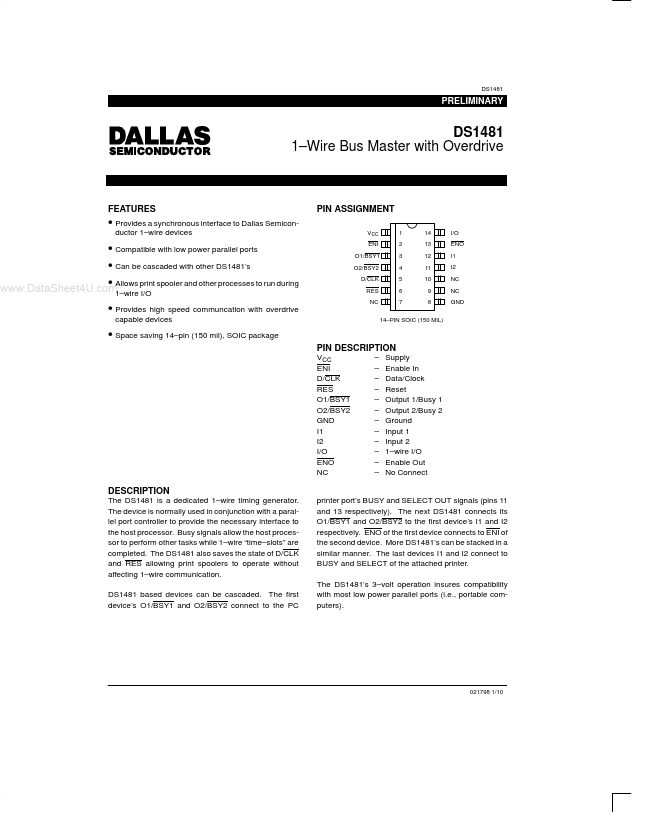

- Supply Enable In Data/Clock Reset Output 1/Busy 1 Output 2/Busy 2 Ground Input 1 Input 2 1-wire I/O Enable Out No Connec