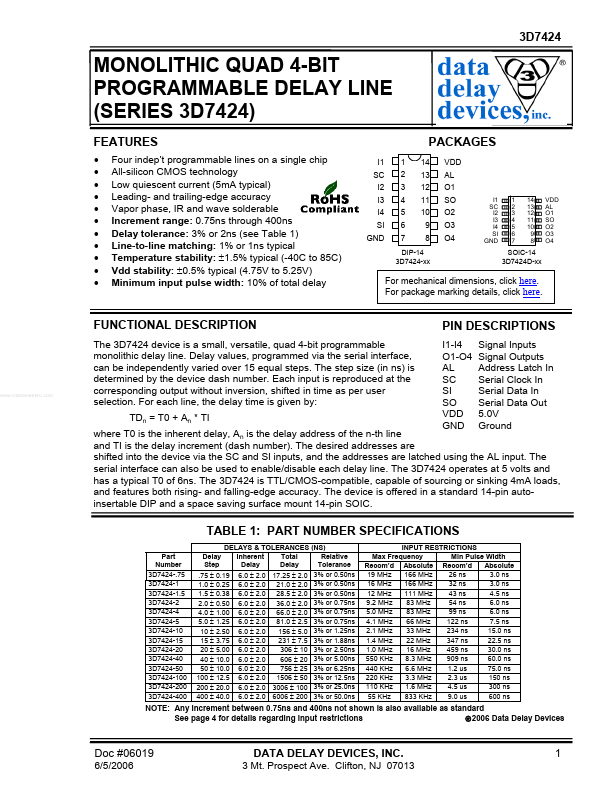

3D7424 Description

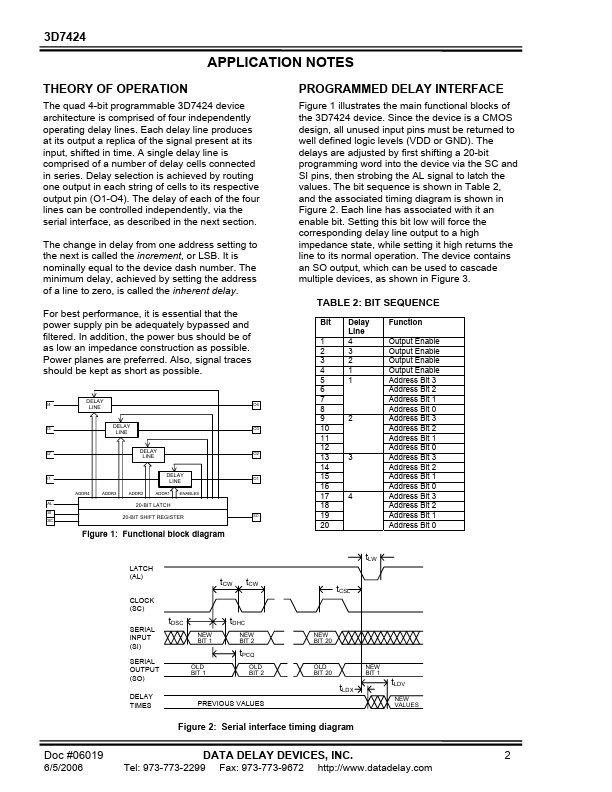

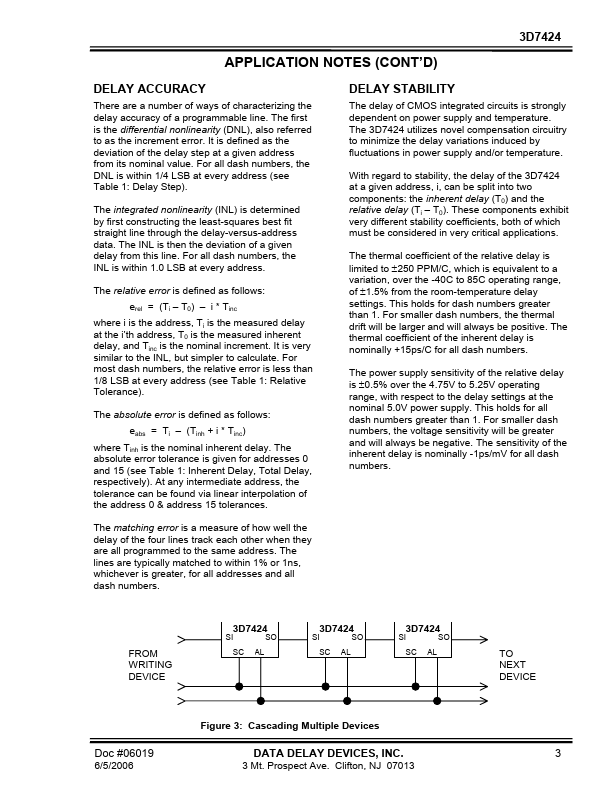

The 3D7424 device is a small, versatile, quad 4-bit programmable monolithic delay line. Delay values, programmed via the serial interface, can be independently varied over 15 equal steps. The step size (in ns) is determined by the device dash number.