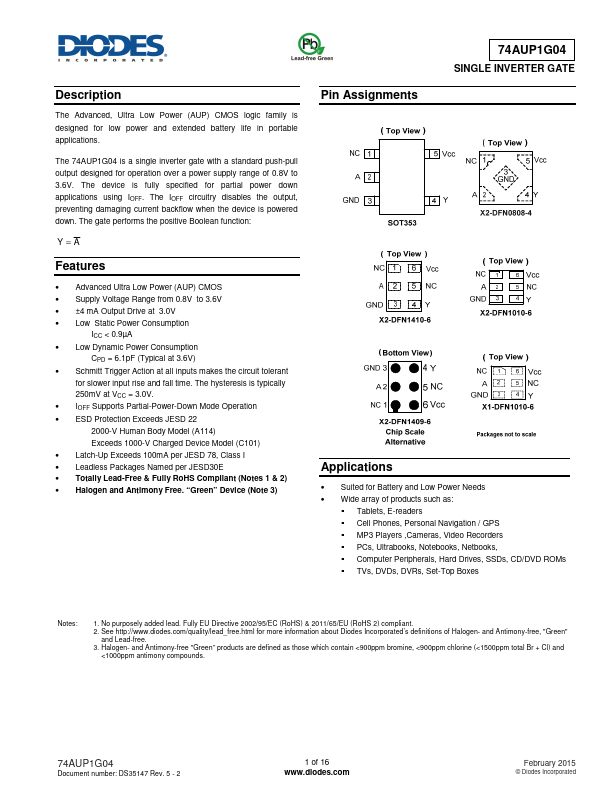

74AUP1G04 Overview

Key Specifications

Package: TSSOP

Mount Type: Surface Mount

Pins: 5

Operating Voltage: 1.8 V

Description

The Advanced, Ultra Low Power (AUP) CMOS logic family is designed for low power and extended battery life in portable applications. The 74AUP1G04 is a single inverter gate with a standard push-pull output designed for operation over a power supply range of 0.8V to 3.6V.

Key Features

- Advanced Ultra Low Power (AUP) CMOS

- Supply Voltage Range from 0.8V to 3.6V

- ±4 mA Output Drive at 3.0V

- Low Static Power Consumption ICC < 0.9µA

- Low Dynamic Power Consumption CPD = 6.1pF (Typical at 3.6V)