74AVC1T45

74AVC1T45 is SINGLE BIT DUAL POWER SUPPLY TRANSLATING TRANSCEIVER manufactured by Diodes Incorporated.

Description

The 74AVC1T45 is a single bit, dual supply transceiver with tri-state outputs suitable for transmitting a single logic bit across different voltage domains. The A input/output pin is designed to track VCCA while the B input/output tracks VCCB. This arrangement allows for universal low-voltage translation between any voltages from 1.2V to 3.6V. The Direction pin (DIR) controls the direction of the transceiver and in a logic voltage related to VCCA. When a high logic level is applied to DIR the A pin bees an input and the B pin bees the output. Conversely the roles of A and B are reversed when DIR is asserted low.

The tri-state feature occurs when either of the power supply voltages are zero. This is also an Ioff feature and allows for the output to remain in a high-impedance state with both power supplies at 0V preventing damaging backflow currents and providing power down electrical isolation up to 3.6 V as not to interfere with any logic activity on pin A or B.

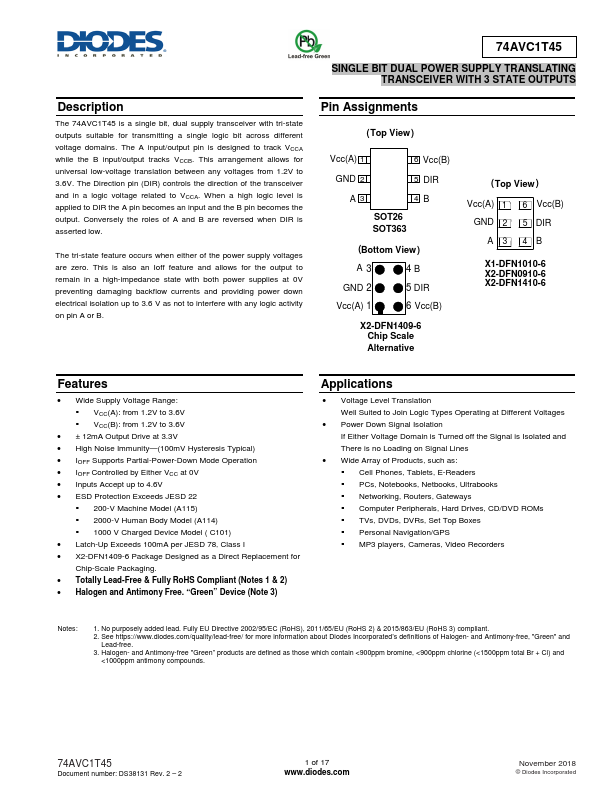

Pin Assignments

(Top View )

Vcc(A) 1 GND 2

6 Vcc(B) 5 DIR

A3 4B

SOT26 SOT363

(Bottom View)

A 3 4B

GND 2

5 DIR

Vcc(A) 1

6 Vcc(B)

X2-DFN1409-6 Chip Scale Alternative

(Top View )

Vcc(A) 1 GND 2 A3

6 Vcc(B) 5 DIR 4B

X1-DFN1010-6 X2-DFN0910-6 X2-DFN1410-6

Features

- Wide Supply Voltage Range:

- VCC(A): from 1.2V to 3.6V

- VCC(B): from 1.2V to 3.6V

- ± 12m A Output Drive at 3.3V

- High Noise Immunity- (100m V Hysteresis Typical)

- IOFF Supports Partial-Power-Down Mode Operation

- IOFF Controlled by Either VCC at 0V

- Inputs Accept up to 4.6V

- ESD Protection Exceeds JESD 22

- 200-V Machine Model (A115)

- 2000-V Human Body Model (A114)

- 1000 V Charged Device Model ( C101)

- Latch-Up Exceeds 100m A per JESD 78, Class I

- X2-DFN1409-6 Package Designed as a Direct Replacement for Chip-Scale Packaging.

- Totally Lead-Free & Fully Ro HS pliant (Notes 1 & 2)

- Halogen and Antimony Free. “Green” Device (Note 3)

Applications

- Voltage Level Translation Well Suited to Join Logic Types Operating at...