74LV132AS14 Overview

Key Specifications

Package: SOP

Mount Type: Surface Mount

Pins: 14

Operating Voltage: 3.3 V

Description

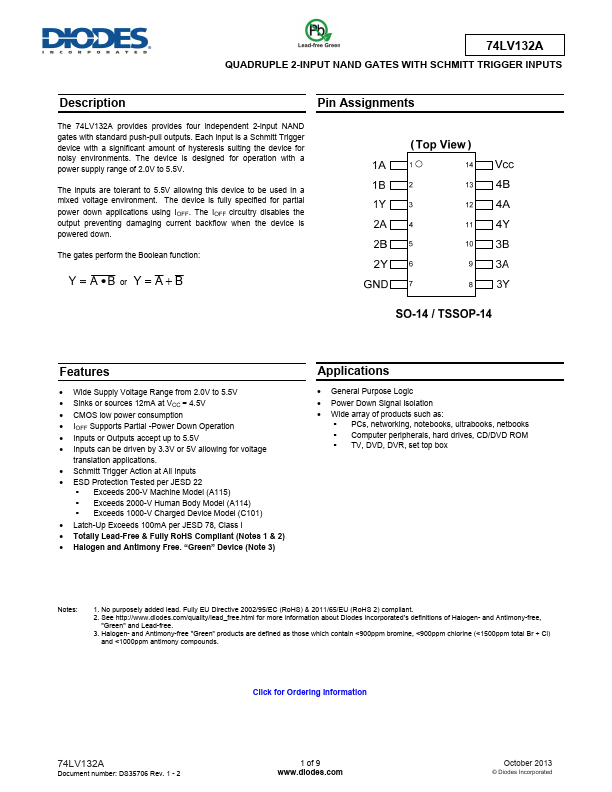

Pin Assignments The 74LV132A provides provides four independent 2-input NAND gates with standard push-pull outputs. Each input is a Schmitt Trigger device with a significant amount of hysteresis suiting the device for noisy environments.

Key Features

- Wide Supply Voltage Range from 2.0V to 5.5V

- Sinks or sources 12mA at VCC = 4.5V

- CMOS low power consumption

- IOFF Supports Partial -Power Down Operation

- Inputs or Outputs accept up to 5.5V