DL5064

Overview

The DL5000 is the industry’s first Fast Field Programmable Gate Array (FFPGA™) family. Utilizing a breakthrough in field programmable interconnect techniques called Active Repeaters, this family provides unprecedented system level performance.

- Fast Field Programmable Gate Arrays™ Patented Active Repeater™ Architecture Data and Clock Rates up to 270 MHz Complex operations up to 200 MHz Input Block Register Setup Time 800 ps Output Block Register Clock-to-out 1.6 ns ECL, PECL and GTL Interface Levels 100K and 100KH Compatible Differential Outputs 1,000 to 10,000 Gates 6 Low-skew Clock Trees Highly Predictable, Fanout Independent Routing Delays

- SRAM-based Programming

- JTAG Boundary Scan

- Fully Automatic Implementation Using DynaTool™ * * * * * * * * * *

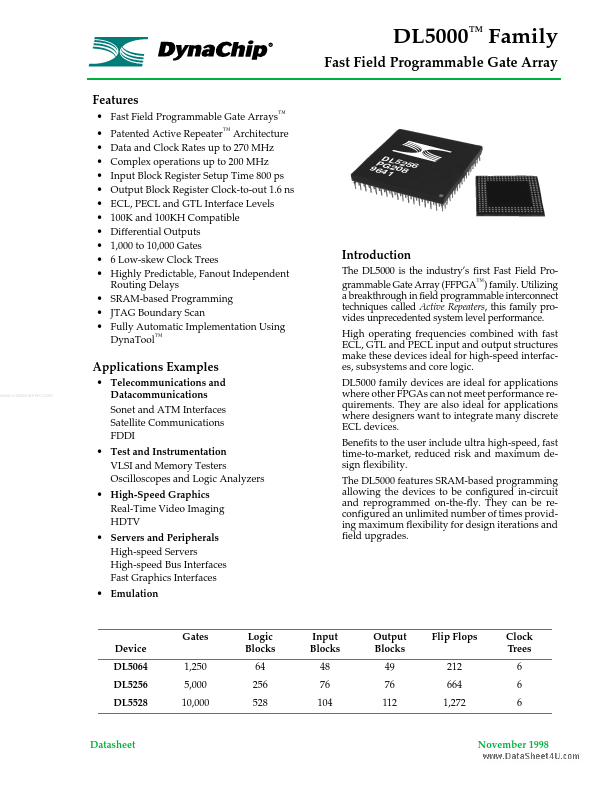

- DL5 2 PG 20 56 964 1 8 Introduction The DL5000 is the industry’s first Fast Field Programmable Gate Array (FFPGA™) family. Utilizing a breakthrough in field programmable interconnect techniques called Active Repeaters, this family provides unprecedented system level performance. High operating frequencies combined with fast ECL, GTL and PECL input and output structures make these devices ideal for high-speed interfaces, subsystems and core logic. DL5000 family devices are ideal for applications where other FPGAs can not meet performance requirements. They are also ideal for applications where designers want to integrate many discrete ECL devices. Benefits to the user include ultra high-speed, fast time-to-market, reduced risk and maximum design flexibility. The DL5000 features SRAM-based programming allowing the devices to be configured in-circuit and reprogrammed on-the-fly. They can be reconfigured an unlimited number of times providing maximum flexibility for design iterations and field upgrades.