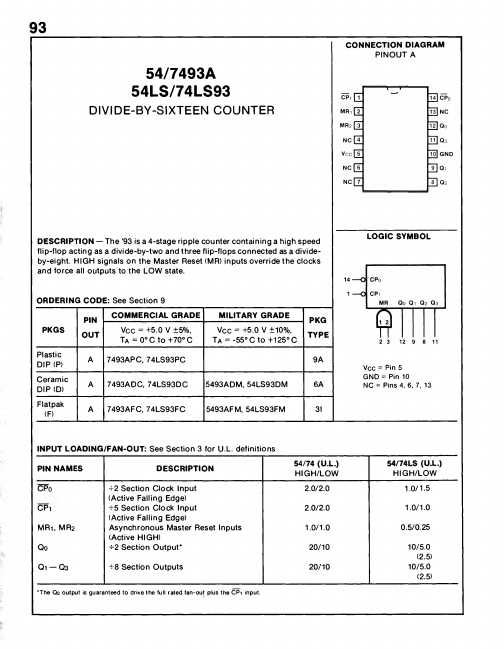

74LS93

DESCRIPTION

- The ’93 is a 4-stage ripple counter containing a high speed flip-flop acting as a divide-by-two and three flip-flops connected as a divideby-eight. HIGH signals on the Master Reset (MR) inputs override the clocks and force all outputs to the LOW state.

ORDERING CODE: See Section 9

PKGS

PIN OUT

MERCIAL GRADE

Vcc = +5.0 V ±5%, Ta = 0°C to +70° C

MILITARY GRADE

Vcc = +5.0 V ±10%, Ta = -55° C to +125° C

PKG TYPE

Plastic DIP (P)

A 7493APC, 74LS93PC

9A

Ceramic DIP (D)

A 7493ADC, 74LS93DC 5493ADM, 54LS93DM

6A

Flatpak (F)

A 7493AFC, 74LS93FC

5493AFM, 54LS93FM

3I

LOGIC SYMBOL

Vcc = Pin 5 GND = Pin 10 NC = Pins 4, 6, 7, 13

INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

PIN NAMES

DESCRIPTION

CPo CPi MRi, MR2 Qo

-s-2 Section Clock Input (Active Falling Edge) -^-5 Section Clock Input (Active Falling Edge) Asynchronous Master Reset Inputs (Active HIGH) -j-2 Section Output-

Qi

- Q3

+Q Section Outputs

54/74 (U.L.) HIGH/LOW

2.0/2.0 2.0/2.0

1.0/1.0...