UPD4564163

UPD4564163 is 64M-bit SDRAM manufactured by Elpida Memory.

- Part of the UPD4564841 comparator family.

- Part of the UPD4564841 comparator family.

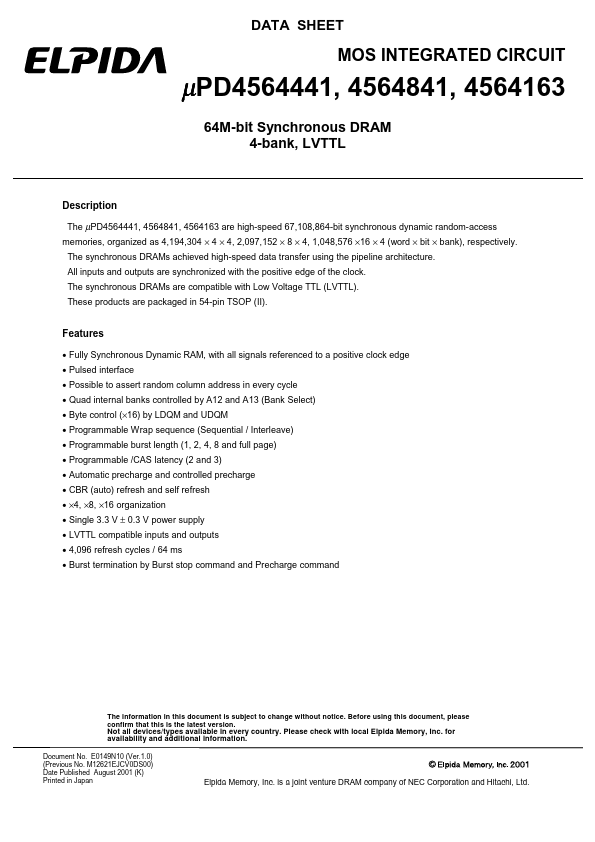

DATA SHEET

MOS INTEGRATED CIRCUIT

µPD4564441, 4564841, 4564163

64M-bit Synchronous DRAM 4-bank, LVTTL

Description

The µPD4564441, 4564841, 4564163 are high-speed 67,108,864-bit synchronous dynamic random-access memories, organized as 4,194,304 × 4 × 4, 2,097,152 × 8 × 4, 1,048,576 ×16 × 4 (word × bit × bank), respectively. The synchronous DRAMs achieved high-speed data transfer using the pipeline architecture. All inputs and outputs are synchronized with the positive edge of the clock. The synchronous DRAMs are patible with Low Voltage TTL (LVTTL). These products are packaged in 54-pin TSOP (II).

Features

- Fully Synchronous Dynamic RAM, with all signals referenced to a positive...