XRK79892 Description

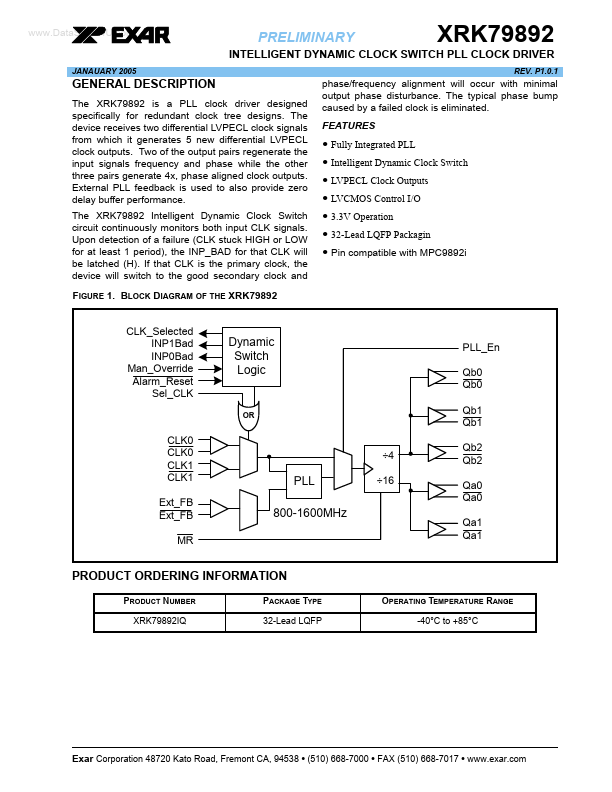

The XRK79892 is a PLL clock driver designed specifically for redundant clock tree designs. The device receives two differential LVPECL clock signals from which it generates 5 new differential LVPECL clock outputs. Two of the output pairs regenerate the input signals frequency and phase while the other three pairs generate 4x, phase aligned clock outputs.

XRK79892 Key Features

- Fully Integrated PLL

- Intelligent Dynamic Clock Switch

- LVPECL Clock Outputs

- LVCMOS Control I/O

- 3.3V Operation

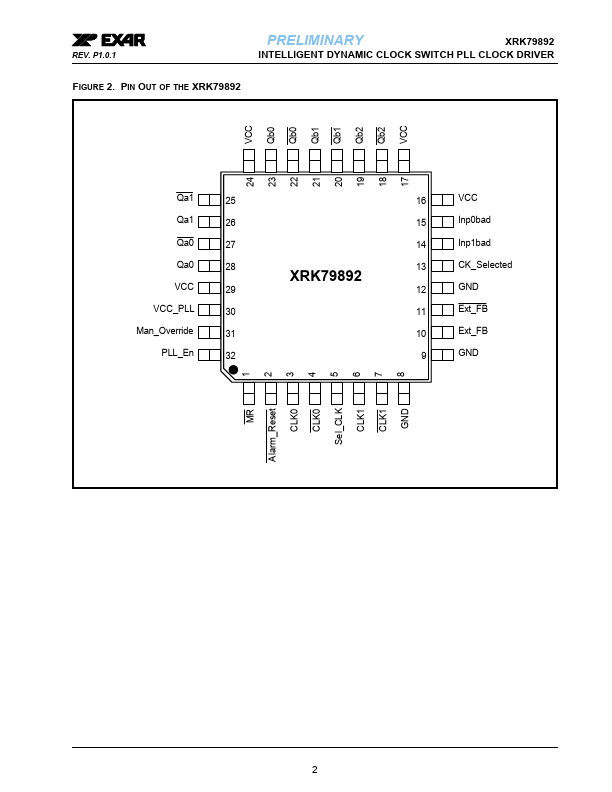

- 32-Lead LQFP Packagin

- Pin patible with MPC9892i

- (510) 668-7000

- FAX (510) 668-7017