74LVX573 Overview

Key Specifications

Package: SOP

Mount Type: Surface Mount

Pins: 20

Operating Voltage: 2.7 V

Description

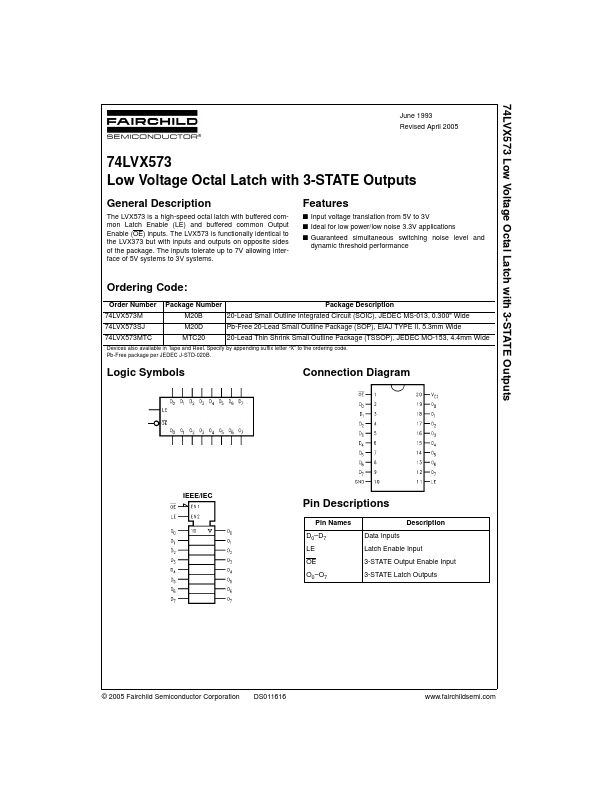

The LVX573 is a high-speed octal latch with buffered common Latch Enable (LE) and buffered common Output Enable (OE) inputs. The LVX573 is functionally identical to the LVX373 but with inputs and outputs on opposite sides of the package.

Key Features

- Specify by appending suffix letter “X” to the ordering code

- Pb-Free package per JEDEC J-STD-020B

- Logic Symbols Connection Diagram IEEE/IEC Pin Descriptions Pin Names D0–D7 LE OE O0–O7