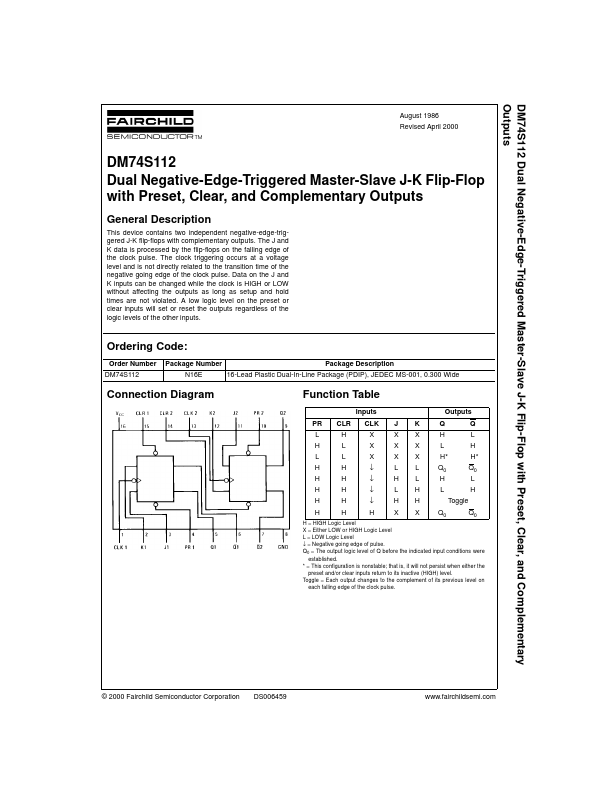

- Part: 74S112

- Description: Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flop

- Manufacturer: Fairchild Semiconductor

- Size: 42.41 KB

Related Fairchild Semiconductor Datasheets

| Part Number | Description |

|---|---|

| 74S138 | Decoder/Demultiplexer |

| 74S139 | Decoder/Demultiplexer |

| 74S140 | Dual 4-Input NSND Line Driver |

| 74S153 | Dual 1-of-4 Line Data Selector/Multiplexer |

| 74S157 | Quad 1 of 2 Line Data Selectors/Multiplexers |