DM74ALS253

Overview

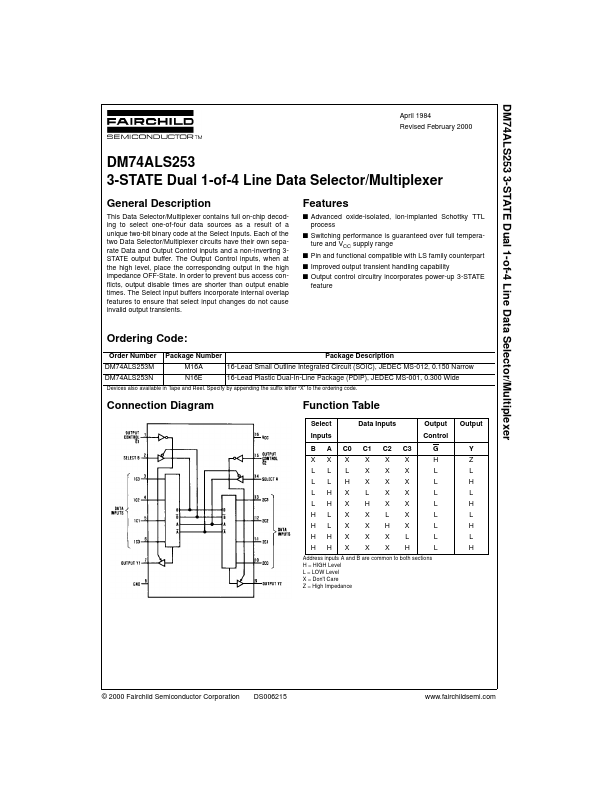

This Data Selector/Multiplexer contains full on-chip decoding to select one-of-four data sources as a result of a unique two-bit binary code at the Select Inputs. Each of the two Data Selector/Multiplexer circuits have their own separate Data and Output Control inputs and a non-inverting 3STATE output buffer.