DM74S112

DM74S112 is Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flop manufactured by Fairchild Semiconductor.

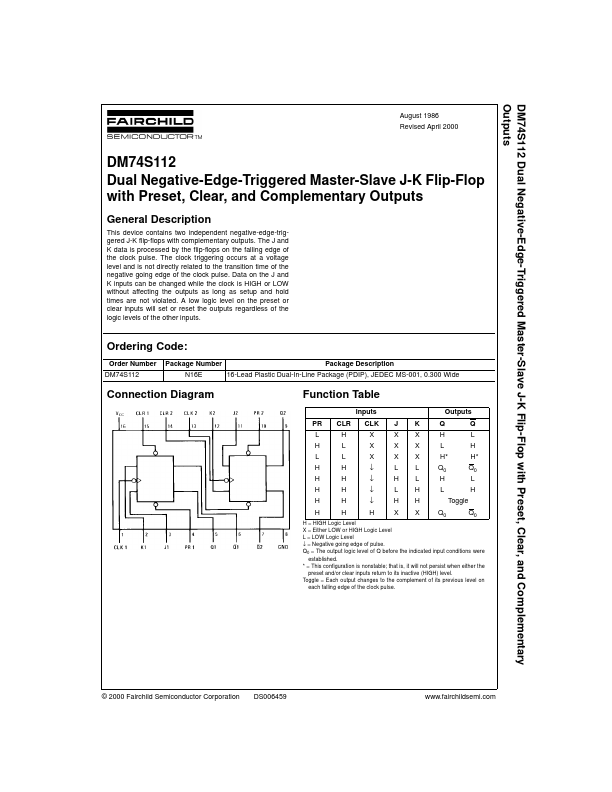

DM74S112 Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flop with Preset, Clear, and plementary Outputs

August 1986 Revised April 2000

Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flop with Preset, Clear, and plementary Outputs

General Description

This device contains two independent negative-edge-triggered J-K flip-flops with plementary outputs. The J and K data is processed by the flip-flops on the falling edge of the clock pulse. The clock triggering occurs at a voltage level and is not directly related to the transition time of the negative going edge of the clock pulse. Data on the J and K inputs can be changed while the clock is HIGH or LOW without...