FQD3P50TM_F085

Overview

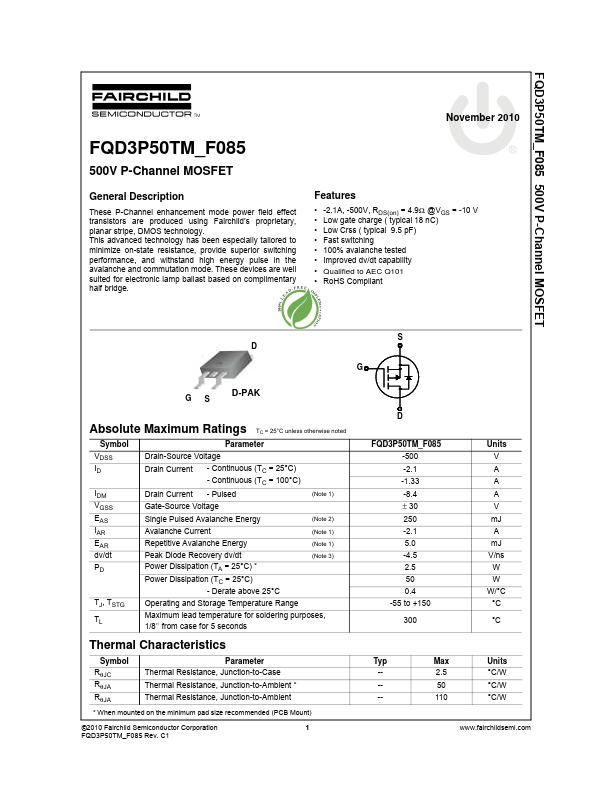

These P-Channel enhancement mode power field effect transistors are produced using Fairchild’s proprietary, planar stripe, DMOS technology. This advanced technology has been especially tailored to minimize on-state resistance, provide superior switching performance, and withstand high energy pulse in the avalanche and commutation mode.

- -2.1A, -500V, RDS(on) = 4.9Ω @VGS = -10 V

- Low gate charge ( typical 18 nC)

- Low Crss ( typical 9.5 pF)

- Fast switching

- 100% avalanche tested

- Improved dv/dt capability

- Qualified to AEC Q101

- RoHS Compliant S D! GS D-PAK