MC100ES6014

Features

- -

- -

- -

- -

- 25 ps Within Device Skew 400 ps Typical Propagation Delay Maximum Frequency > 2 GHz Typical The 100 Series Contains Temperature pensation PECL and HSTL Mode: VCC = 2.375 V to 3.8 V with VEE = 0 V ECL Mode: VCC = 0 V with VEE =

- 2.375 V to

- 3.8 V LVDS and HSTL Input patible Open Input Default State 20-Lead Pb-Free Package Available

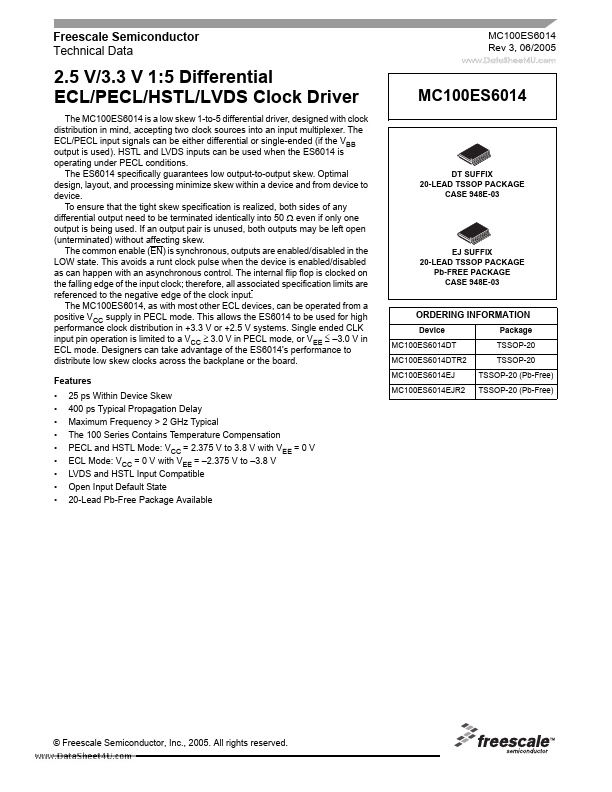

DT SUFFIX 20-LEAD TSSOP PACKAGE CASE 948E-03

EJ SUFFIX 20-LEAD TSSOP PACKAGE Pb-FREE PACKAGE CASE 948E-03

ORDERING INFORMATION

Device MC100ES6014DT MC100ES6014DTR2 MC100ES6014EJ MC100ES6014EJR2 Package TSSOP-20 TSSOP-20 TSSOP-20 (Pb-Free) TSSOP-20 (Pb-Free)

© Freescale Semiconductor, Inc., 2005. All rights reserved.

VCC 20

EN 19

VCC 18

CLK1 17

CLK1 16

VBB 15

CLK0 14

CLK0 CLK_SEL 13 12

VEE 11

..

1 Q0

2 Q0

3 Q1

4 Q1

5 Q2

6 Q2

7 Q3

8 Q3

9 Q4

10 Q4

Warning: All VCC and VEE pins must be externally connected to Power Supply to guarantee proper operation.

Figure 1. 20-Lead Pinout (Top...