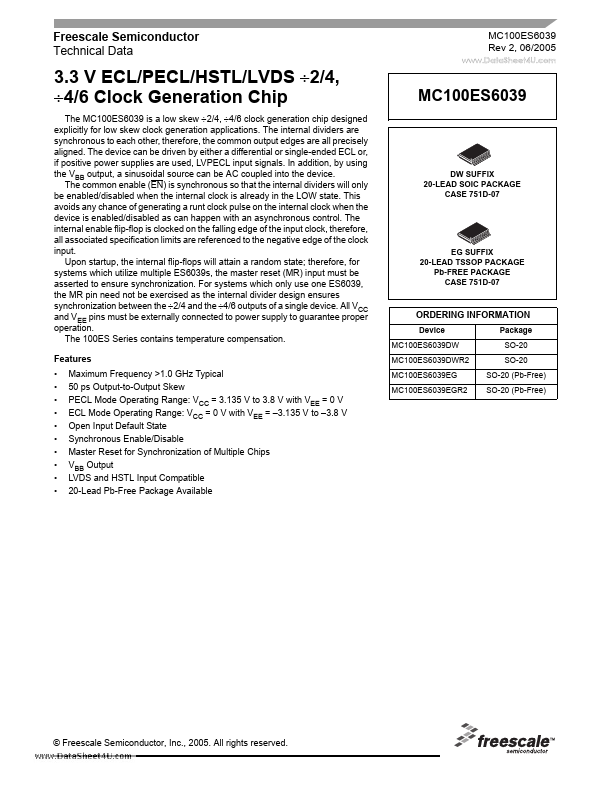

MC100ES6039

Overview

- Maximum Frequency >1.0 GHz Typical 50 ps Output-to-Output Skew PECL Mode Operating Range: VCC = 3.135 V to 3.8 V with VEE = 0 V ECL Mode Operating Range: VCC = 0 V with VEE = -3.135 V to -3.8 V Open Input Default State Synchronous Enable/Disable Master Reset for Synchronization of Multiple Chips VBB Output