MB85R4M2T

FEATURES

Copyright©2013 FUJITSU SEMICONDUCTOR LIMITED All rights reserved 2013.11

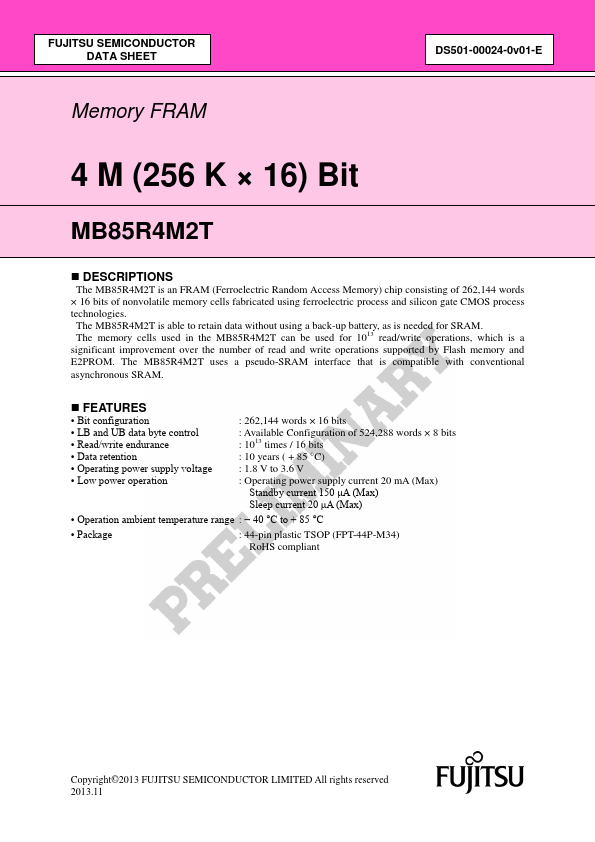

- PIN ASSIGNMENTS

(TOP VIEW)

A4 A3 A2 A1 A0 / CE I/ O0 I/ O1 I/ O2 I/ O3 VDD VSS I/ O4 I/ O5 I/ O6 I/ O7 / WE A17 A16 A15 A14 A13 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 A5 A6 A7 / OE / UB / LB I/ O15 I/ O14 I/ O13 I/ O12 VSS VDD I/ O11 I/ O10 I/ O9 I/ O8 / ZZ A8 A9 A10 A11 A12

FPT- 44P- M34

DS501-00024-0v01-E

- PIN DESCRIPTIONS

Pin Number 1 to 5, 18 to 22, 23 to 27, 42 to 44 Pin Name A0 to A17 Functional Description

Address Input pins Select 262,144 words in FRAM memory array by 18 Address Input pins. When these address inputs are changed during /CE equals to “L” level, reading operation of data selected in the address after transition will start. Data Input/Output pins These are 16 bits bidirectional pins for reading and writing. Chip Enable Input pin In case the /CE equals to “L” level and...