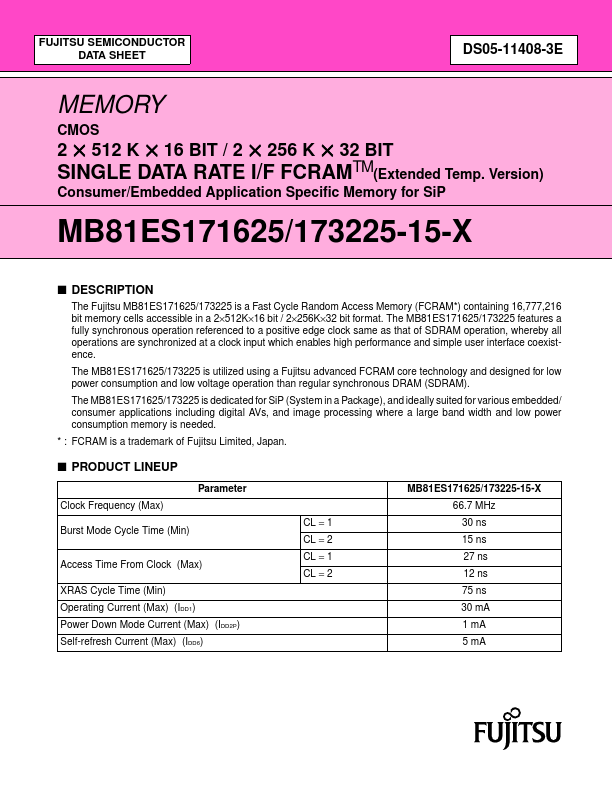

MB81ES171625

Overview

- FCRAM core with Single Data Rate SDRAM interface

- 512 K word × 16 bit × 2 bank or 256 K word × 32 bit × 2 bank organization

- Single +1.8 V Supply ±0.15 V tolerance

- CMOS I/O interface

- Programmable burst type, burst length, and CAS latency Burst type : Sequential Mode, Interleave Mode Burst length : 1, 2, 4, 8, full column (64 : ×16 bit, 32 : ×32 bit) CAS latency MB81ES171625/173225-15-X CL = 1 (Min tCK = 30 ns, Max 33.3 MHz)