GS8662TT38BGD

GS8662TT38BGD is 72Mb SigmaDDR-II+ Burst of 2 SRAM manufactured by GSI Technology.

- Part of the GS8662TT20BD comparator family.

- Part of the GS8662TT20BD comparator family.

165-Bump BGA mercial Temp Industrial Temp

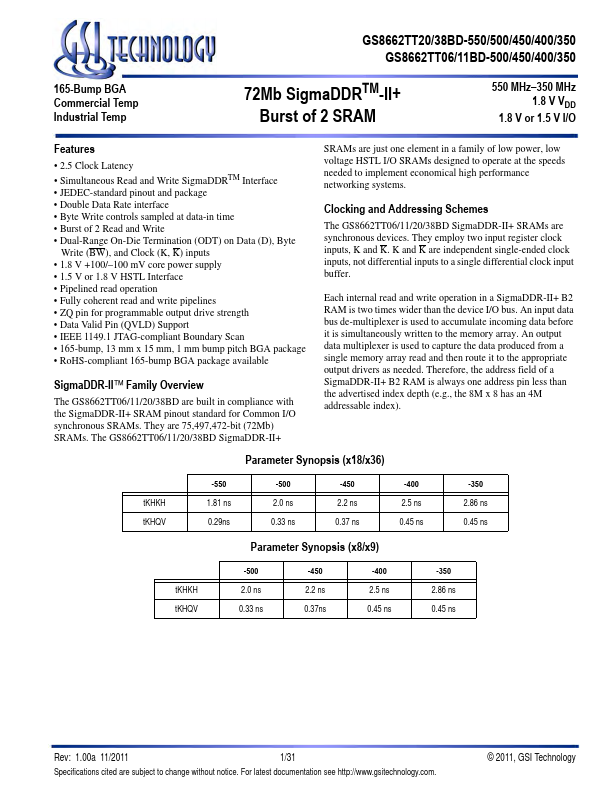

GS8662TT20/38BD-550/500/450/400/350 GS8662TT06/11BD-500/450/400/350

72Mb SigmaDDRTM-II+ Burst of 2 SRAM

550 MHz- 350 MHz 1.8 V VDD

1.8 V or 1.5 V I/O

Features

- 2.5 Clock Latency

- Simultaneous Read and Write SigmaDDRTM Interface

- JEDEC-standard pinout and package

- Double Data Rate interface

- Byte Write controls sampled at data-in time

- Burst of 2 Read and Write

- Dual-Range On-Die Termination (ODT) on Data (D), Byte

Write (BW), and Clock (K, K) inputs

- 1.8 V +100/- 100 mV core power supply

- 1.5 V or 1.8 V HSTL Interface

- Pipelined read operation

- Fully coherent read and write pipelines

- ZQ pin for programmable output drive strength

-...