HI-3200 Overview

Key Specifications

Package: DIP

Operating Voltage: 15 V

Max Operating Temp: 75 °C

Min Operating Temp: 0 °C

Description

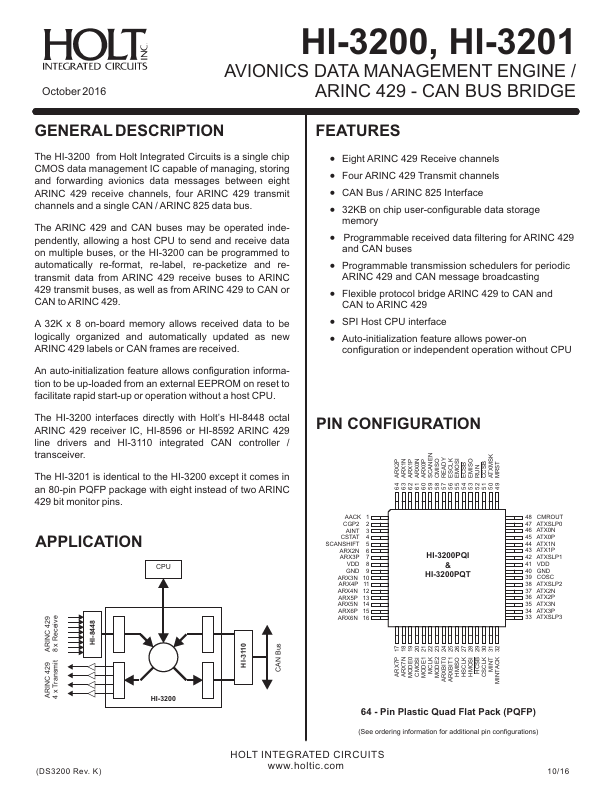

The HI-3200 from Holt Integrated Circuits is a single chip CMOS data management IC capable of managing, storing and forwarding avionics data messages between eight ARINC 429 receive channels, four ARINC 429 transmit channels and a single CAN / ARINC 825 data bus. The ARINC 429 and CAN buses may be operated independently, allowing a host CPU to send and receive data on multiple buses, or the HI-3200 can be programmed to automatically re-format, re-label, re-packetize and retransmit data from ARINC 429 receive buses to ARINC 429 transmit buses, as well as from ARINC 429 to CAN or CAN to ARINC 429.

Key Features

- Eight ARINC 429 Receive channels

- Four ARINC 429 Transmit channels

- CAN Bus / ARINC 825 Interface

- 32KB on chip user-configurable data storage memory

- Programmable received data filtering for ARINC 429 and CAN buses

- Programmable transmission schedulers for periodic ARINC 429 and CAN message broadcasting

- Flexible protocol bridge ARINC 429 to CAN and CAN to ARINC 429

- SPI Host CPU interface

- Auto-initialization feature allows power-on configuration or independent operation without CPU