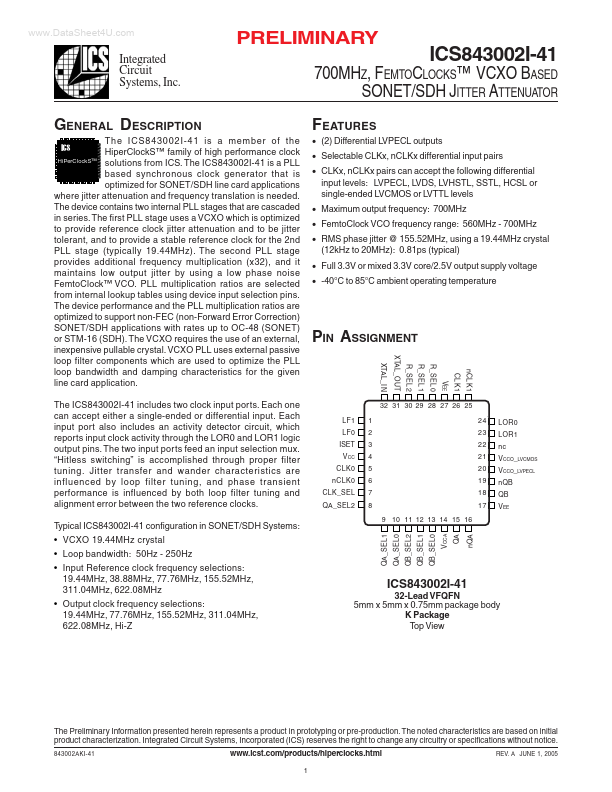

ICS43002I-41 Key Features

- (2) Differential LVPECL outputs

- Selectable CLKx, nCLKx differential input pairs

- CLKx, nCLKx pairs can accept the following differential input levels: LVPECL, LVDS, LVHSTL, SSTL, HCSL or single-ended L

- Maximum output frequency: 700MHz

- FemtoClock VCO frequency range: 560MHz

- 700MHz

- RMS phase jitter @ 155.52MHz, using a 19.44MHz crystal (12kHz to 20MHz): 0.81ps (typical)

- Full 3.3V or mixed 3.3V core/2.5V output supply voltage

- 40°C to 85°C ambient operating temperature