ICS889874

Overview

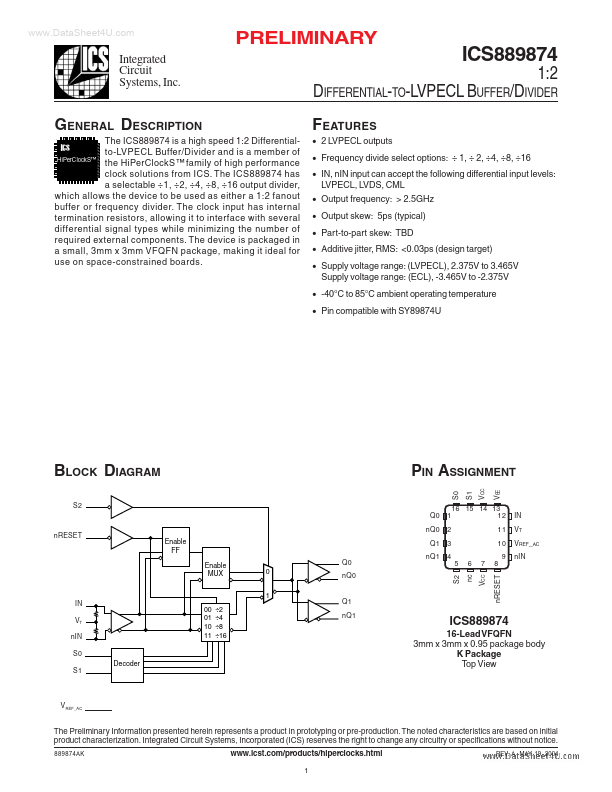

The ICS889874 is a high speed 1:2 Differentialto-LVPECL Buffer/Divider and is a member of HiPerClockS™ the HiPerClockS ™ family of high performance clock solutions from ICS. The ICS889874 has a selectable ÷1, ÷2, ÷4, ÷8, ÷16 output divider, which allows the device to be used as either a 1:2 fanout buffer or frequency divider.

- 2 LVPECL outputs

- Frequency divide select options: ÷ 1, ÷ 2, ÷4, ÷8, ÷16

- IN, nIN input can accept the following differential input levels: LVPECL, LVDS, CML

- Output frequency: > 2.5GHz

- Output skew: 5ps (typical)

- Part-to-part skew: TBD

- Additive jitter, RMS: <0.03ps (design target)

- Supply voltage range: (LVPECL), 2.375V to 3.465V Supply voltage range: (ECL), -3.465V to -2.375V

- -40°C to 85°C ambient operating temperature

- Pin compatible with SY89874U