ICS889872

ICS889872 is DIFFERENTIAL-TO-LVDS BUFFER/DIVIDER W/INTERNAL TERMINATION manufactured by IDT.

Features

- -

- -

- -

- -

- -

- -

Three LVDS outputs Frequency divide select options: ÷4, ÷6: >2GHz, ÷8, ÷16: >1.6GHz IN, n IN input can accept the following differential input levels: LVPECL, LVDS, CML Output frequency: >2GHz Cycle-to-cycle jitter: 1ps (typical) Total jitter: 10ps (typical) Output skew: 7ps (typical), QA/n QA outputs Part-to-part skew: 250ps (typical) Propagation Delay: 750ps (typical), QA/n QA outputs Full 2.5V supply mode -40°C to 85°C ambient operating temperature Available in both standard (Ro HS 5) and lead-free (Ro HS 6) packages

General Description

The ICS889872 is a high speed Differential-to LVDS Buffer/Divider w/Internal Termination and is a Hi Per Clock S™ member of the Hi Per Clock S™family of high performance clock solutions from IDT. The ICS889872 has a selectable ÷2, ÷4, ÷8, ÷16 output dividers. The clock input has internal termination resistors, allowing it to interface with several differential signal types while minimizing the number of required external ponents. The device is packaged in a small, 3mm x 3mm VFQFN package, making it ideal for use on space-constrained boards.

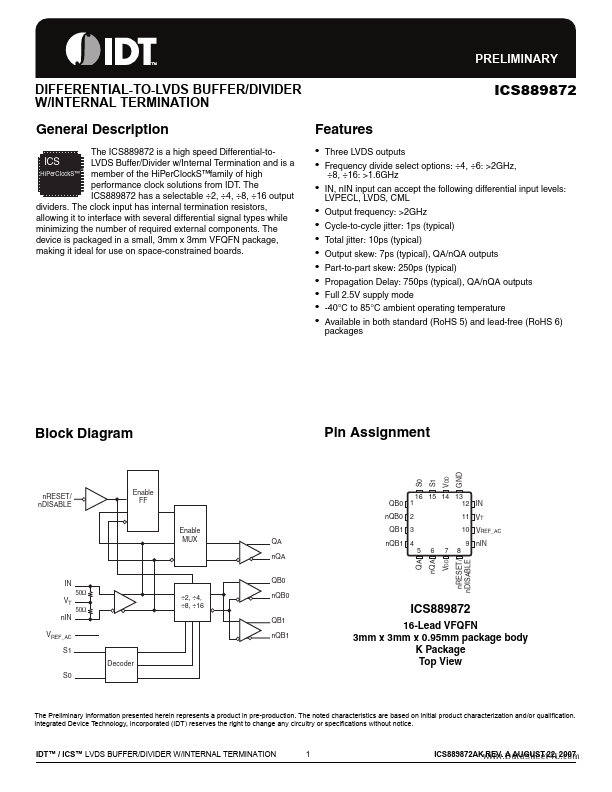

Block Diagram

Pin Assignment

GND n RESET/ n DISABLE

Enable FF

QB0 1 n QB0 Enable MUX 2

16 15 14 13 12 IN 11 VT 10 VREF_AC 9 n IN 5

QB1 3 QA n QA n QB1 4 6 n QA

S0

S1

8 n RESET/ n DISABLE

50Ω

QB0 ÷2, ÷4, ÷8, ÷16 n QB0

VT n IN VREF_AC S1 Decoder S0

50Ω

QB1 n QB1

16-Lead VFQFN 3mm x 3mm x 0.95mm package body K Package Top View

The Preliminary Information presented herein represents a product in pre-production. The noted characteristics are based on initial product characterization and/or qualification. Integrated Device Technology, Incorporated (IDT) reserves the right to change any circuitry or specifications without notice.

IDT™ / ICS™ LVDS BUFFER/DIVIDER W/INTERNAL TERMINATION

ICS889872AK REV. A AUGUST 22, 2007

ICS889872 DIFFERENTIAL-TO-LVDS BUFFER/DIVIDER W/INTERNAL TERMINATION

PRELIMINARY

Table 1. Pin Descriptions

Number 1, 2...